Power Systems Design: Empowering Global Innovation

SPECIAL REPORT: POWERING COMMUNICATIONS (Pg 39)

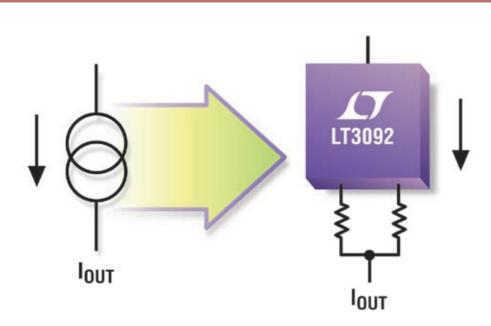

# Finally

### A Simple, Precise 2-Terminal Current Source

The simplest functions are often the most difficult to design. The current source—a basic circuit element—has not been available as an IC. Discrete implementations suffer from poor accuracy, high TC or complexity. Our new current source, the LT®3092, provides all the performance without the compromises: programmable up to 200mA, high AC and DC impedance, low TC and no capacitors required. Its two floating terminals make it easy to use in precision or remote current limiting, bias circuits, intrinsic safety circuits, temperature sensing, active load and signaling applications.

#### **Features**

- 0.5mA to 200mA Output Current

- No Capacitors Required

- 10ppm/V Regulation

- 1.2V to 40V Input Voltage

- Reverse Voltage & Current Protection

- Thermal Protection

- 1% SET Pin Current Accuracy

- 3mm x 3mm DFN-8, 8-Lead ThinSOT™ and 3-Lead SOT-223 Packages

# Current Accuracy vs Temperature 1.00 0.75 0.50 0.25 -0.50 -0.75 -1.00 -50 -25 0 25 50 75 100 125 150

www.linear.com/3092

+49-89-962455-0

www.linear.com/LTspice

27, LTC, LT, LTM, µModule and LTspice are registered trademarks and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Europe Sales offices: France 33-1-41079555 Italy 39-02-38093656 Germany 49-89-9624550 Sweden 46-8-623-1600 UK 44-1628-477066 Finland 3589-988733699 Distributors: Belguim ACAI 32-0-2-7205983 Finland Tech Data 358-98733382 France Arrow Electronique 33-1-49-784978, Tekelec Airtronic 33-1-56302425 Germany Insight 49-89-611080.

Temperature (°C)

Setron 49-531-80980 Ireland MEMEC 353-61-411842 Israel Avnet Components 972-9-778-0351 Italy Silverstar 39-02-66125-1 Netherlands ACAL 31-0-402502602 Spain Arrow 34-91-304-3040 Turkey Arrow Elektronik 90-216-4645090 UK Arrow Electronics 44-1234-791719, Insight Memec 44-1296-330061

# Find It Here. digikey.com/europe

The industry's broadest product selection available for immediate delivery

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order.

Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

#### **2SP0115T Gate Driver**

Unleash the full power of your converter design using the new 2SP0115T Plug-and-Play driver. With its direct paralleling capability, the scalability of your design into highest power ratings is unlimited. Rugged SCALE-2 technology enables the complete driver functionality on a single PCB board, exactly fitting

the size of 17mm dual modules. Combined with the CONCEPT advanced active clamping function, the electrical performance of the IGBT can be fully exploited while keeping the SOA of the IGBT. Needless to say that the high integration level provides the best possible reliability by a minimzed number of components.

#### Features

Plug-and-Play solution 1W output power 15A gate current <100ns delay time ± 4ns jitter Advanced active clamping Direct- and halfbridge mode Direct paralleling capability 2-level and multilevel topologies DIC-20 electrical interface Safe isolation to EN50178 UL compliant 50.- USD @ 1000 pieces

Power Systems Design: Empowering Global Innovation

#### WWW.POWERSYSTEMSDESIGN.COM

Visit us online for exclusive content; Industry News, Products, Reviews, and full PSD archives and back issues.

#### **VIEW**point

The Communications Conundrum By Cliff Keys, Editorial Director & Editor-in-Chief, PSDE

#### **POWER**line

Dual Cool™ Package for High Power Density

#### **POWER**player

Powering Wireless Communications By Fred Zust, Integrated Device Technology

#### **MARKET**watch

In-Flight Connectivity is Here to Stay By Matthew Towers, IMS Research

#### **DESIGN**tips

Power Supply Development Diary Part VIII By Dr. Ray Ridley, Ridley Engineering

#### **COVER STORY**

Powering Communications By Patrick Le Fevrě, Ericsson

#### **TECHNICAL FEATURES**

#### 21 Power Modules

Optimizing Power Modules, By Werner Obermaier, Vincotech

#### Thermal Management

Thermoelectric Energy, By Dave Koester, Nextreme

#### Power Supplies

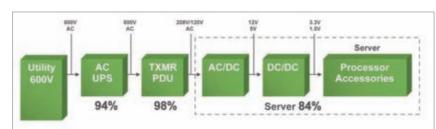

Power Efficiency Breakthrough, By John Stephens, Future Electronics

#### High Reliability

Designer's Perspective, By Eric Marcelot, High Rel Semiconductor

#### 34 Energy Efficiency

Optimized Industrial Systems PSUs, By Graham Proud, CamSemi

#### SPECIAL REPORT:

**Powering Communications**

#### Communications Power Solutions

By Wayne Seto, Fairchild

#### Comms Continuity

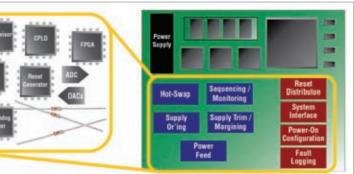

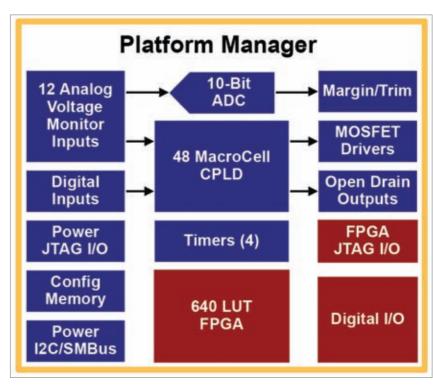

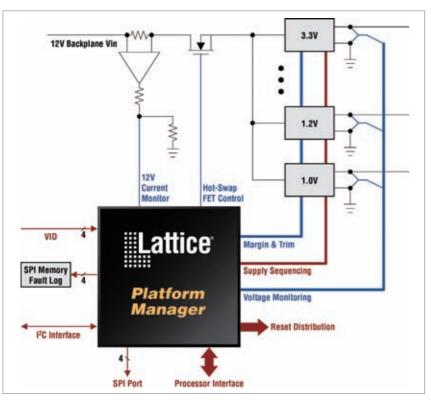

By Shyam Chandra, Lattice

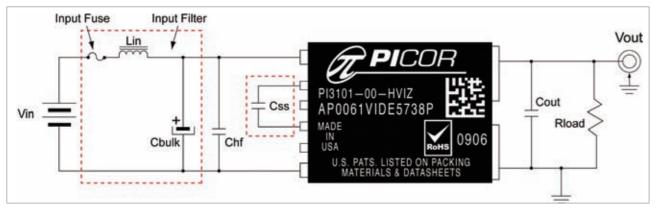

#### 47 Compact Isolated DC-DC Converter

By Christopher Swartz, Picor Corporation

#### Hidden Costs of Power Distribution

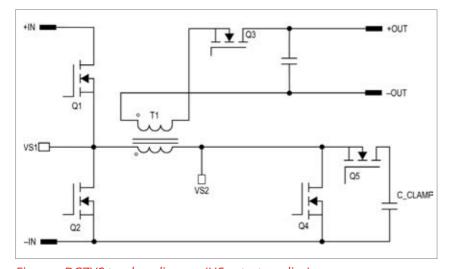

By Ed Spears, Eaton

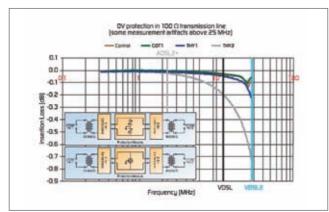

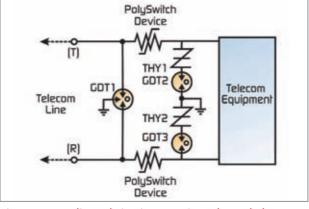

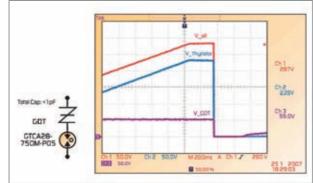

#### Telecommunications Safety

By Matthew Williams, Tyco

Highlighted Products News, Industry News and more web-only content, to:

#### www.powersystemsdesign.com

#### CAREERdevelopment

Communications Field Calls on Analog Designers and Power Specialists,

By David G. Morrison, Editor, How2Power.com

#### GREENpage

Clean Networking Reported By Cliff Keys, Editor-in-Chief, PSDE

#### 60 Dilbert

146 Charles Street Annapolis, MD 21401 USATel: +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### Editorial Director & Editor-in-Chief

cliff.keys@powersystemsdesign.com

#### **Contributing Editors**

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research Ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineerng.com

David Morrison, How2Power david@how2power.com

#### **Publishing Director**

Jim Graham jim.graham@powersystemsdesign.com

Iulia Stocks Julia.stocks@powersystemsdesign.com

#### **Circulation Management**

Kathryn Phillips Kathryn.phillips@powersystemsdesign.com

#### **Research Director**

Meghan Corneal Meghan.corneal@powersystemsdesign.com

#### Magazine Design Louis C. Geiger

louis@agencyofrecord.com

#### **Production Manager**

Leo Jiang leow@action-new.net

Registration of copyright: January 2004ISSN number: 1613-6365

AGS Media Group and Power Systems Design Europe magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or omissions in the materia contained herein regardless of whether such errors result from negligence, accident or any other cause whatsoever.

Send address changes to:circulation@powersystemsdesign.com.

Free Magazine Subscription,go to: www.powersystemsdesign.com

Volume 7, Issue 9

# THE **COMMUNICATIONS** CONUNDRUM

Welcome this special issue of PSD where we run a feature on 'Powering Communications'. We hope you like the new look of our magazine and the advanced features of our new website.

It is just incomprehensible to imagine the way we live and work today without the richness and connectivity that modern communications systems provide. We can be connected by our cell phones, tablet PCs, computers and even our home entertainment systems as never before. Communications systems need to provide a wealth of features and dependable bandwidth, all of which require sophisticated power management for base, remote or portable operation.

Powering these feature-and-connectivity-rich devices with increasing demand on power, and importantly, its management has become a critical issue. Manufacturers want to differentiate and provide their customers with a wide variety of applications and yet the power unit, normally a battery, has a very limited capacity. Battery technology is not moving as fast as we would like and therefore engineers must be frugal in their designs.

Global subscribers to wideband telco services such as Fiber To The Home (FTTH) and VDSL are expected to rise at more than triple the rate of ADSL during the next few years as carriers seek to boost their networks' performance, according to iSuppli Corp. The telco broadband market is undergoing a seismic shift in technology as technologies like ADSL begin to give way to wideband services like FTTH and VDSL. While ADSL will continue to dominate most telcos' broadband installed bases for years to come, subscribership has begun to contract in many developed countries such as the United States, Japan, Korea, Canada and Germany.

Rising competition from other industries is compelling the telcos to turn to wideband technology. Telcos around the world are facing stiff competition from competitive access suppliers, cable providers and wireless operators. This competitive pressure, which has resulted in stagnating revenues and subscribers eroding by as much as 10% per year, has caused telephone companies to rethink how they do business in the residential space. Virtually all carriers, as well as competitive access suppliers, have chosen a strategy of deploying value-added services, such as IPTV, in combination with their core residential business of voice and data in order to stop subscriber erosion and to increase subscriber Average Revenue Per User (ARPU).

Among bandwidth-intensive applications, IPTV is one of the few that has proven to be successful with subscribers. However, telcos plan to offer other services to boost revenue during the next few years, including 3-D HDTV, cloud-based Digital Video Recording (DVR), distance learning, video telephony, home automation and remote home networking management.

Enjoy the issue. Your feedback is valuable to us, and do check out Dilbert at the back of the magazine.

All the best,

Editorial Director & Editor-in-Chief, Power Systems Design Cliff.Keys@powersystemsdesign.com

### Does your digital power-supply design require high performance flexible on-chip peripherals?...

### **Control complex Digital Power applications and save power**

Microchip's new dsPIC33F 'GS' Series DSCs provide on-chip peripherals including high-speed Pulse-Width-Modulators (PWMs), ADCs and analogue comparators, specifically designed for high performance, digital power supplies.

The powerful dsPIC33F 'GS' series is specifically aimed at power control applications and can be configured for a variety of topologies, giving power-supply designers the complete freedom to optimise for specific product applications. Multiple independent power control channels enable an unprecedented number of completely independent digital control loops. The dsPIC33F 'GS' series offers the optimal digital power solution supported by royalty free reference designs and advanced power design tools.

Typical applications of the new 'GS' series DSC include: Lighting (HID, LED, fluorescent), uninterruptable power supplies, intelligent battery chargers, AC-DC and DC-DC power converters, solar and pure sine-wave inverters, induction cooking, and power factor correction.

- Digital control loops with 12 to 18 high-speed, 1 ns resolution PWMs

- Up to 24 channels 10-bit on-chip ADCs

- 2 to 4 Million samples per second (MSPS) ADC for low latency and high-resolution control

- Pin range 64 to 100

- Memory 32 to 64KB Flash memory

dsPIC33F 'GS' Series Plug-In Module – MA330024

#### **GET STARTED IN 3 EASY STEPS**

- 1. Purchase a new 'GS' Series Plug-In Module

- 2. Download Digital Power Reference Design

- 3. Order samples and start designing! www.microchip.com/SMPS

### **Intelligent Electronics start with Microchip**

www.microchip.com/smps

# DUAL COOL™ PACKAGE FOR HIGH POWER DENSITY

As DC-DC applications, such as power modules, telecommunications and servers become more space-constrained; designers are looking for ever smaller devices to meet their design challenges. The thermal capability of these devices, however, is a vital concern.

n order to meet the needs for high current capability, high efficiency and smaller form factors, Fairchild

Semiconductor developed the Dual

Cool™ packaging for MOSFETs.

The Dual Cool package is a top-side cooling PQFN device that incorporates new packaging technology which enables additional power dissipation through the top of the package as well as the bottom.

Dual Cool packaging features an exposed heat slug that delivers a significant reduction in thermal resistance from junction to top of case, resulting in more than 60 percent higher power dissipation capability than standard PQFN packaging when a heat sink is mounted. Additionally, MOSFETs in the Dual Cool package are designed with Fairchild's proprietary PowerTrench® process technology, that enables lower RDS(ON) and higher load currents in smaller package sizes.

Unlike competitive top-side cooling solutions, these devices are currently available in both Power33

(3.3mm x 3.3mm) and Power56 (5mm x 6mm) Dual Cool packaging options. Maintaining the same industry-standard PQFN footprint, the Dual Cool package allows power engineers to rapidly qualify MOSFETs in Dual Cool packaging, gaining increased thermal efficiency without the need to adjust for non-standard packages.

Devices currently available in the Dual Cool package include the FDMS2504SDC, FDMS2506SDC, FDMS2508SDC, FDMS2510SDC (5mm x 6mm footprint) and the FDMC766oDC (3.3mm x 3.3mm footprint). These devices are ideal as synchronous rectifying MOSFETs for DC-DC converters, telecom secondary side rectification and high end server/workstation applications. Fairchild's Dual Cool packaged MOSFETs' top-side cooling and an ultra-low junction temperature (Rthja) enable increased thermal efficiency. MOSFETs in the Dual Cool package can be used with or without a heat sink.

These Dual Cool packaged MOSFETs are part of Fairchild's

industry-leading MOSFET portfolio. By understanding the demands for higher current DC-DC power supplies in smaller footprints for space constrained applications, as well as the company's customers and the markets they serve, Fairchild can tailor its unique combination of functional, process and packaging innovation into solutions that make a real difference in electronic designs.

With this enhanced dual path thermal performance and improved parasitics over its wire-bonded predecessors, the use of a heat sink with Dual Cool packaging provides even more impressive results. Test results show a heatsinked Dual Cool package allows synchronous Buck converters to deliver higher output current, thus increasing power density. With Fairchild's world-class trench silicon technology, Dual Cool packaging proves to be a clear leader in power density and thermal performance.

For more information on Fairchild's Dual Cool package, visit:

www.fairchildsemi.com/dualcool

#### THE PA107DP, MP103FC HIGH SPEED, HIGH VOLTAGE LINEAR AMPLIFIERS

Cirrus Logic power linear amplifiers, featuring the technology of Apex Precision Power, make designing with power simple! The PA107DP delivers a 3,000 V/µs slew rate to drive piezo actuators with ground breaking speed. The MP103FC is a dual amplifier with 15 A of output current per channel and a 180 V/µs slew rate to drive slower piezos but with multiple drivers.

- · High speed rail-to-rail 3,000 V/µs (PA107DP), 180 V/µs (MP103FC)

- · High power bandwidth 230 kHz

- · Wide dual supply voltage 30 V to 200 V (MP103FC), 40 V to 200 V (PA107DP)

- High PEAK output current 5 A (PA107DP), 15 A (MP103FC)

The superior quality and reliability of these off-the-shelf solutions can eliminate design cycle headaches and speed your time to market.

www.cirrus.com/107psde

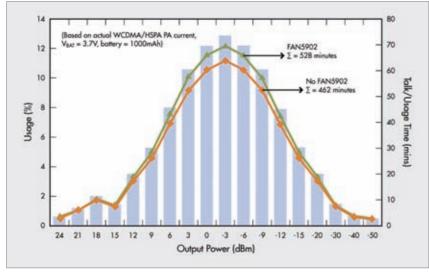

# POWERING WIRELESS COMMUNICATIONS

By Fred Zust

The recent increased demand for 3G smart phones and wireless-enabled PDA-type devices will continue to drive the increase of mobile

data traffic in the enterprise and consumer market spaces. The requirement for more data consumption for a richer multimedia experience will encourage service providers to add higher capacity 3.5G and 4G base stations to their existing wireless infrastructure mix, be they WiMAX or 3G LTE.

n 3.5G and 4G base station architectures, the increasing data rate and the push for a higher capacity of users per base station led to increasing backplane speeds between radio and baseband cards. This overall bandwidth increase, in turn, requires more multi-core digital signal processors (DSPs) interconnected in a standard cluster configuration on the baseband card with FPGAs and embedded processors in a peerto-peer networking cluster.

Multi-core DSPs now offer architectures with three to six cores, operating in the Gigahertz-per-core range. Data rates between processing elements and the back plane can range from 1 gigabit to as high as 10Gbps, all of which are supported by semiconductors that use the RapidIO 1.3 standard. Continued demands for greater bandwidth have resulted in a market

need for higher data rates between processing elements, while at the same time, maintaining low latency, deterministic reliable packet delivery plus an easy-to-manage memory map. All of these are attributes supported by RapidIO 1.3

The above market drivers led to the Serial RapidIO® 2.1 standard. Leading wireless infrastructure equipment providers are adopting this technology in their nextgeneration platform designs to increase overall system performance and support more subscribers per base station with more revenuegenerating, real-time multimedia features. But Serial RapidIO 2.1 is not limited to the rollout of new platforms or upgrades of base stations to 4G standards.

In some cases, Serial RapidIO 2.1 is ideal for cost-reduction and power-saving measures in legacy platform

updates because Serial RapidIO 2.1 can support more bandwidth per serial link, doubling the baud rate on a link from 3.125Gbaud in Serial RapidIO 1.3 to 6.25Gbaud in Serial RapidIO 2.1. Moreover, it can be transmitted up to 100cm over two connectors, making it ideal for cascading multiple chassis co-located in one physical rack, immediately expanding the processing capacity of a base station.

Serial RapidIO 2.1 also adds support for Virtual Channels (VCs) and Virtual Output Queuing (VOQs), improving overall traffic management and allowing OEMs to support more bandwidth in the network with differentiated classes of service, ideal for 4G networks being developed today.

Improvements to Quality of Service (QoS) will appeal to carrier-grade

communications applications. Within the physical layer, the new standard additions receive equalization capabilities that will allow it to support extended longreach (100cm) traces at the full data rate. This can even be done with conventional FR4-based PC board materials.

In embedded systems, all of the above features are only supported by RapidIO. While 10 Gigabit Ethernet offers some of the attributes that RapidIO 2.1 offers, given that it originates from the LAN/WAN networks, using it in multiprocessor embedded systems for peer-to-peer processing can be difficult due to

its higher latency, non-deterministic packet delivery, large packets sizes (causing system-level congestion) and large processor overhead in terminating the protocol, reducing processor cycles for application implementation. The 10 Gigabit Ethernet raw data rate is only half of what is available with Serial RapidIO 2.1. Wireless system OEMs, as well as those in other embedded markets, have chosen to continue from their existing RapidIO 1.3 investments and are moving forward with Serial RapidIO 2.1.

The continuous advances in the wireless infrastructure create the need for significant increases in

system capability and bandwidth. The industry has responded with the evolution of its most successful interface standard to meet the needs for more bandwidth, more flexibility and better quality of service. Serial RapidIO 2.1 addresses all of these needs and maintains backward compatibility with the previous versions of the specification — helping to keep the installed infrastructure base from becoming obsolete.

Author: Fred Zust

Vice President & General Manager,

Communications Division

Integrated Device Technology

www.idt.com

# Brand\_new\_Design

WWW.POWERSYSTEMSDESIGN.COM

# IN-FLIGHT CONNECTIVITY IS HERE TO STAY

By Matthew Towers

Historically, the aerospace market has been something of a niche, with most electronics confined to cockpit and flight operations functions,

and addressed by specialist electronics manufacturers.

n recent years, electronics content has started to mushroom. At first this was driven by growing demand for personal "in-seat" entertainment systems. These were introduced initially into premium cabins but have rapidly moved into economy/coach for long haul travel, providing a plethora of entertainment facilities including video, audio, and gaming. The newest generation of systems from leading suppliers, such as Panasonic and Thales, are more advanced, offering bigger and higher quality displays, new functionality, and better reliability. In the newest Boeing and Airbus aircraft, the cost of the in-flight entertainment system can now sometimes exceed the cost of the engines, thus becoming the second biggest hardware expense after the air-frame.

Looking ahead, further innovation is on the way that will drive even more electronics into the aerospace market. Connectivity is the current buzz-word in the

industry and North American carriers are leading the way when it comes to in-flight Wi-Fi capability. Over 1,000 aircraft are now fitted out with Aircell's Gogo in-flight internet – meaning that approximately one-third of all North American flights offer the ability to go online while in the air. Many more are set to introduce this functionality in the coming years with low-cost carriers Southwest and Jet Blue the latest to announce deals with Row 44 and Viasat respectively.

Although in-flight Wi-Fi on North American flights has now become relatively commonplace, this is not the case in other regions.

That said, a raft of airlines including Lufthansa, Emirates and Cathay Pacific have recently committed to providing access to the internet during flights in the near future, whilst many of the world's biggest airlines are still to make announcements.

However, unlike their US counterparts who are restricted by stringent FCC regulations, airlines operating out of Europe, for example, are able to offer cellular as well as Wi-Fi connectivity onboard their flights. As such, many have partnered with companies able to provide in-flight mobile connectivity such as Aeromobile and OnAir so that their passengers are able to use their mobile phones to text and call in the air.

The introduction of connectivity in the air will offer passengers even greater entertainment options whilst in-flight. Activities such as email, SMS messaging, web-surfing, live TV and on-line shopping will all become a reality. There are, however, still quite a number of issues to resolve. These include:

- Bandwidth bandwidth into and out of the aircraft is still limited and this will restrict functionality initially.

- Investment up-front investment required by the airlines can be large. At a

time when the industry as a whole is not very profitable, this is making some airlines think very carefully before committing.

- Passenger attitudes it is still unclear how passengers will feel about their close neighbour being able to place and receive cell-phone calls whilst in-flight.

- Regulations FCC regulations in the US currently prohibit cell-phone calls in the air whilst over US airspace.

Despite these barriers, it appears that in-flight connectivity is here to stay, and in the longer term will become increasingly sophisticated and widely available.

One potential knock-on effect of the move to in-flight connectivity is that it will drive greater demand for in-seat power. Many airlines expect passengers to take advantage of connectivity in the air using their own devices - whether cell-phones, iPods, notebooks, netbooks or tablets like the iPad. Although battery life for many of these products continues to extend, it will still be highly convenient for passengers to have in-seat power provided so that batteries do not become exhausted or too depleted during long flights.

One thing seems clear. The days of executives "escaping" unconnected into the air for 10

hours, and enjoying some respite from the pressures of phone and email are numbered. Personally, I will be sorry to see them go!

Author: Matthew Towers Senior Research Director -Communications IMS Research

www.imsresearch.cor

WWW.POWERSYSTEMSDESIGN.COM

# POWER SUPPLY DEVELOPMENT DIARY

#### Part VIII

By Dr. Ray Ridley

This article continues the series in which Dr. Ridley documents the processes involved in taking a power supply from the initial design to the full-power prototype. In Part VIII, the

prototype power supply is connected to a real system load and several issues are encountered.

#### **Power Supply Design Schedule**

So far, this series of articles has taken 7 months to present [1]. The actual uninterrupted time spent on the power supply testing and redesign was approximately 160 hours, following the initial completion of the PC board. Many issues have been resolved. Three iterations of the output inductor and four iterations of the power transformer have been built.

There are still issues remaining to be tested, including thermal performance, EMI, and proper control loop design. An estimated 100 hours of testing and data collection will be needed for this phase.

The hours that you will need for your project will vary significantly from this, depending on many factors:

- 1. How much power is being processed.

- 2. Input voltage range.

- 3. Design experience level.

- 4. Prior experience with the specific technology and topology chosen.

I have observed in the past that a good power supply designer will be able to get to production with perhaps three iterations of the printed circuit board. The first iteration should catch the critical issues that compromise the ruggedness of the power supply. As much data as possible should be collected from each board.

The second iteration of the board should be near production-level, depending on the extent of changes needed. The second board will typically be used for thorough thermal testing, EMI testing, and system testing.

The final board will fix any issues encountered to produce a manufactured product. Only minor changes should be needed on the final iteration.

PC board design time can be very variable. For the best designs, the power supply design engineer is intimately involved in the layout process, physically placing all of the critical components manually, and specifying the critical layout paths, power planes, and spacing.

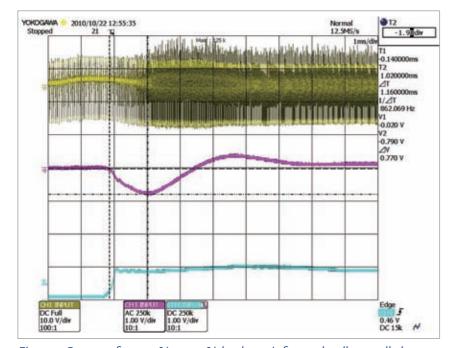

#### **System Testing**

At this stage of the design, the power supply has been tested at full load, and across the full range of input line. Many changes have been made to the board to address the kind of issues that arise with virtually all switching power supplies running off-line. Most of the issues have been related

Figure 1: First-pass PC Board

Connected to System Load

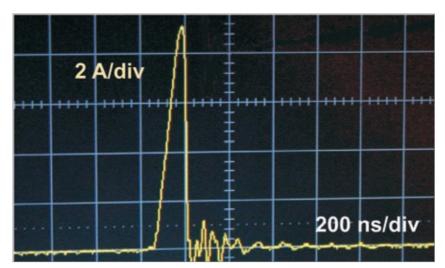

Figure 2: Initial Primary Current with Discharged RCD Clamp Capacitor.

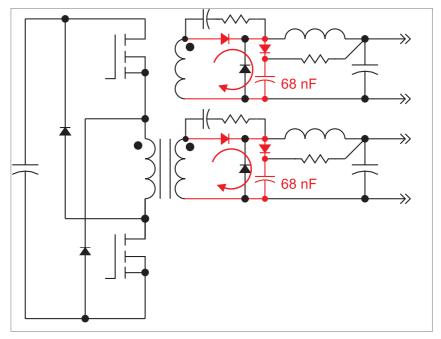

Figure 3: Main Output RCD Clamps.

to the first 200 ns of turn-on of the switch. Controlling overcurrent and overvoltage are paramount to making the power supply rugged. This applies to just about every power supply that is developed.

This is a reasonable point in the project to stop and implement a new PC board design. However, I have always found it very valuable to do preliminary testing with the real system as early as possible. There are always unpredictable issues that can

be encountered.

Figure 1 shows the prototype power supply connected to a power amplifier, the intended load. Remember this is a Revision 1 board, designed for stand-alone testing, so there are lots of wires to connect power supply and load. It is not uncommon for the early prototype to look distinctly low-tech, which sometimes alarms engineering managers who lack experience in power. While the setup is not particularly attractive, there is

great value in performing this kind of testing early on in the power supply development.

Several issues were encountered in this project:

- Power supply would not start when connected with lowimpedance source and real load.

- 2. RCD clamp needed redesign.

- Common-mode EMI interfered with amplifier circuitry, resulting in audible noise.

- Actual load requirements were significantly lower than original specification.

### Power Supply Would Not Start – RCD Clamp Redesign

When the prototype power supply was first connected to its load, an immediate problem was encountered – the power supply would not start. There are two factors leading to this. Firstly, the power supply was being plugged into a very stiff input source, without a variac and power transformer presenting impedance at the input. Secondly, the load has significant internal capacitance, and this looks like a short circuit to the power supply when it first starts.

The main problem was the rapid application of input power. The observed primary current on the first cycle of operation was observed to be very high, as shown in Figure 2. This current looks very similar to the short-circuit current observed earlier in testing, and it was initially suspected that there was a short-circuit in the power supply. However, none were found, but the initial pulse of current continued to trip the second level of current limiting in the UC3825 control chip, initiating a soft-start delay.

After a day of testing, the problem was finally found to be an issue with

WWW.POWERSYSTEMSDESIGN.COM

WWW.POWERSYSTEMSDESIGN.COM

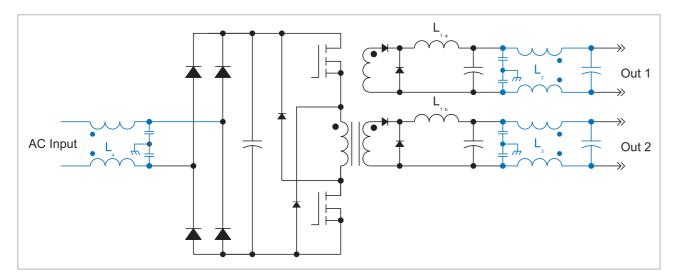

Figure 4: Common-mode Filtering Added to Input Line and Outputs

the RCD snubber on the secondary of the converter. At turn-on, the two secondary RCD clamp capacitors (68 nF each) are completely uncharged. They must be charged up to the reflected input voltage on the secondary, and this results in the high current path shown in red in Figure 3. It only takes a couple of cycles to fully charge this capacitor, but if soft-start is initiated, the capacitor may have discharged again and the converter stays in a hiccup mode of operation with just a single pulse provided on an occasional basis. This is a drawback of the RCD snubber on the secondary side; it must be charged before it can begin to operate properly. Once charged, it has the advantage that there is no turn-on current spike due to this clamp, and it works very effectively.

In this case, the solution was to reduce the value of the RCD capacitor down to 4700 pF, a reduction of more than ten times.

Notice, however, that this will not fix the problem for every power supply. It depends on the input voltage, leakage inductance of the transformer (lower leakage results in a higher spike), and the rate of application of input voltage. This is yet another problem encountered during the first 200 ns of switch turn-on. It did not show up in earlier testing since the rise time of the input voltage was limited by the series impedance of an isolation transformer and a variac. [3]

#### **EMI Components**

The next issue encountered is with EMI. The output noise on the power supply interacted with the load system and its grounding, resulting in audible noise from the output of the system. I have been on many consulting jobs where this was a major issue, and it can often be expected with switching power supplies.

Space had been designed on the power supply board to accommodate a second stage filter [2], but I often like to design both a commonmode, and differential-mode filter in the same element for the outputs of a power supply. Figure 4 shows the common-mode filters which were added to the power supply on both the main outputs, and the input line. Once these were added, the measured output ripple was substantially attenuated by the differential- mode action of the filter. The common-mode action of the

filter eliminated the noise from the amplifier.

Only when the chassis ground was connected to all the filters was the noise eliminated. This does not, however, always fix system noise. Sometimes the chassis ground itself can be corrupted with noise, so it is very valuable to conduct this level of system testing before the next iteration of the PC board. It gives a much higher level of confidence for final system integration.

#### Specification Revisited

The final issue encountered in the system was something that happens time and again in our industry. The power supply load was not the same as the original specification. In this case, the actual load was considerably less than the original 350 W anticipated. Electronics systems designers are notorious for overestimating the load current actually required. (Although, of course, it is sometimes underestimated, and that can present much more of a problem to the power supply designer.)

This is another great advantage of doing the real load test early in the design. The system designers may

not be ready for your power supply, and they may balk at giving you a system to test, but you finally get to measure the real current requirements for yourself, and confirm that your design is adequate.

In this case, the system testing presents an opportunity for a major redesign which will save parts and money. Four outputs are needed for the amplifier, the original intent being to do this with two separate supplies. However, given the quality of the cross-regulation, and the lowered output requirements of the real system, there is the possibility of designing a four-output power supply using the coupled inductor.

This is a major change to the design, and one which presents a significant layout challenge. Total layout time for the new board was 55 hours.

Changes like this are very common in the power supply industry. You have to remain flexible, and have technology and circuits available to rapidly respond to changing user needs. The specification for a power supply is a living document, and something that is never really complete until the power supply is in production.

#### Summary

When developing a switching power supply, it is important to test the supply with the real load. If possible, you should do this before the second iteration of a PCB since several changes can be anticipated as a result of system testing. In this design example, the system testing pointed to a major redesign opportunity, and such changes should be expected during custom power supply development.

#### References

- "Power Supply Development Diary Parts 1-VII", Ray Ridley, Power Systems Design Magazine, 2010. www.powersystemsdesign.com

- 2. "Second-Stage Output Filter Design", Ray Ridley, Switching Power Magazine, 2001. www. switchingpowermagazine.com.

- 3. "Testing Offline Power Supplies", Ray Ridley, Power Systems Design Magazine, February 2010. www.powersystemsdesign.com

www.ridleyengineering.com

### TDK-EPC

# Superior solutions for IT & communications

- Miniaturized SAW filters for all systems

- LTCC modules for cellular multiband and WLAN

- Application-specific EMI/ESD filter modules

- CeraDiode® 0201 and 0402 for ESD protection

- Surge arresters and varistors for all systems

- Interface transformers, supply transformers and chokes for DSL applications and base stations

- PTC thermistors for line protection

- SMD NTC thermistors for temperature management and compensation

- EMC filter modules for base stations

- Miniaturized MEMS microphones with excellent performance

- Low ESL multilayer ceramic chip capacitors for IC decoupling

www.tdk-epc.com

# POWERING COMMUNICATIONS

#### Digital power techniques set new standards for flexibility

#### By Patrick Le Fèvre

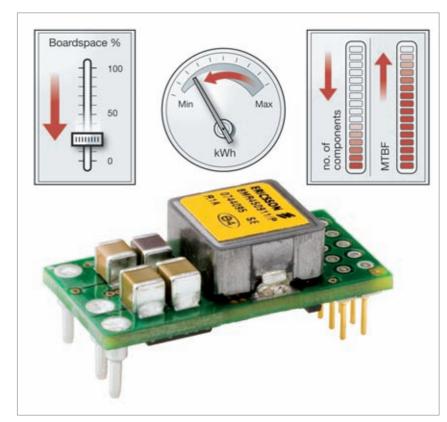

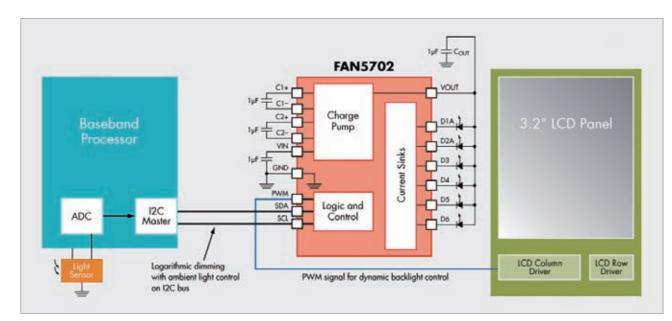

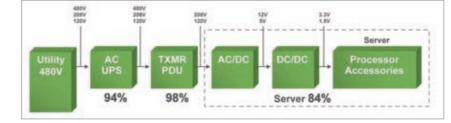

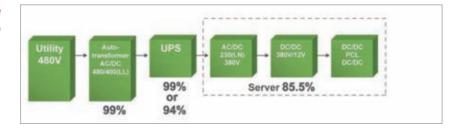

Since the origin of mobile communication, various techniques based on software and hardware have been implemented to optimize energy efficiency. In every telecommunication system there are DC/DC converters and point-of-load conversion systems. The latest generation of power-modules embeds digital cores with communication interfaces to add a new functional dimension – flexibility.

ollowing a gestation period of several decades, digital power control techniques are rapidly gaining market share as designers increasingly appreciate the advantages that the technology offers over its analog counterpart. Despite even more uncertain economic times than those of today, estimates made by power industry analysts in August 2009 awarded digital power an approximately 20% compound annual growth rate for the next five years, and the likelihood is that this figure was somewhat pessimistic—the same analysts thought 45% more appropriate just twelve months previously. Forecast accuracy apart, the key to any technology achieving rapid acceptance and sustainable growth lies with delivering tangible benefits at competitive cost.

As many designers have discovered, the combination of digital power control and digital power management exceeds routine evolutionary expectations to represent a real, cost-effective step change in overall capability. Here, digital power control refers to implementing the inner control loop of a power converter with digital circuitry rather than using familiar analog schemes. For a simple buck converter, this means substituting an analog-to-digital converter for the traditional error-signal feedback amplifier, and deriving correction for the

Source: Ericsson

pulse-width modulator that drives the power switches using digital signal processing techniques in place of a voltage reference, ramp generator, and comparator.

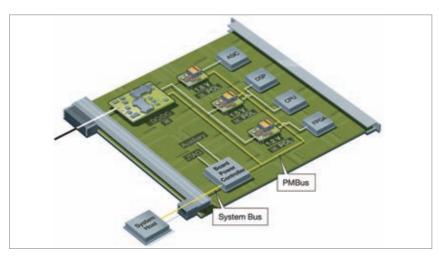

By contrast, digital power management denotes supervisory and control circuitry that communicates via a digital I/O scheme, which today almost invariably exploits the PMBus™ interface that has become the power-industry standard. A converter that combines both of these digital power concepts can actively manage its conversion process to optimize efficiency for changing line and load conditions while including all of the power management system within the same package.

#### Digital configurability delivers lifecycle benefits

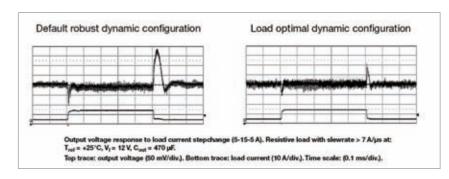

But digital power has much more to offer than bettering the electrical performance and power-density requirements that previously dominated the mindset of power supply designers. Essentially, such performance improvements are due to the ability of a digital control loop to adapt its dynamics to optimally suit line and load conditions in real time; by contrast, passive components set an analog converter's responses, which are inevitably a compromise between stability and dynamic response for the expected operating conditions.

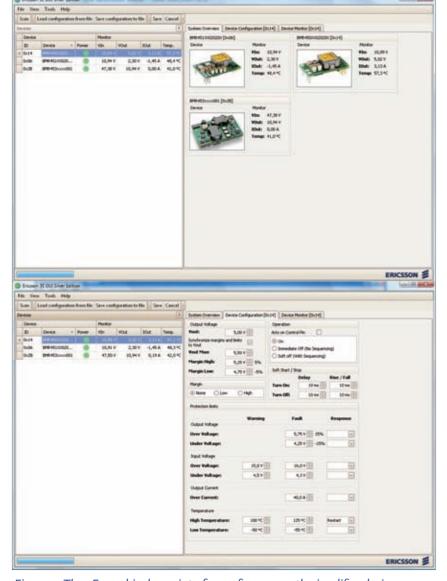

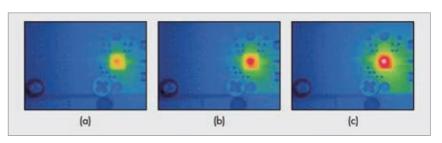

Figure 2: Reprogramming the controlloop constants in a digital power converter can optimize its dynamic performance for a given operating environment

Figure 1: Highly integrated functionalities reduce board-space, increase efficiency and reliability

But in developing its 3E concept that embraces enhanced performance, energy management, and end-user value, Ericsson recognized that digital power could offer benefits that apply throughout a product's lifecycle.

As the digital converter's core is a mixed-signal IC it's possible to pack the supervisory measurement and control hardware together with its PMBus interface onto the same slice of silicon at negligible additional cost. This approach optimizes the electrical coupling between the converter's core and its control system, minimizes power consumption, and slashes the amount of PCB real estate that's necessary to accommodate equivalent functionality using analog-based solutions.

Crucially, it's now possible to configure the digital converter when it is initially made, during the development phase of the powersystem designer's application, at the distributor's depot, when the

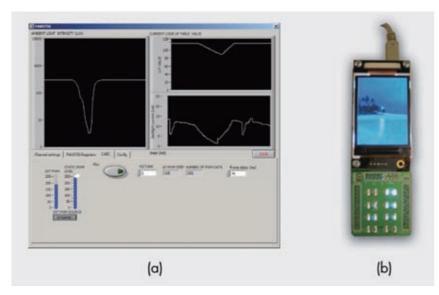

Figure 3: PMBus makes it easy to monitor and control compatible power-system devices such as the 3E family

Figure 4: The 3E graphical user interface software greatly simplifies device configuration

equipment is manufactured, and/or when it is operating within the enduser's equipment. This unparalleled degree of flexibility extends the programmable logic model to the power conversion industry for the first time.

Each 3E family power converter offers an array of programmable parameters that includes output voltage selection, turn-on/off delay times to implement power sequencing for multi-rail loads, slew rate control that provides inrush current protection, voltage margining for system testing, and multiple thresholds for warning and fault conditions for overcurrent, overtemperature, and under- and overvoltage. It's even possible to adjust the response of a digital converter's control loop to optimize its performance for a particular set of load and bulk output capacitance conditions.

Figure 2 shows the result of finetuning the constants that set the responses of a 3E point-of-load regulator's control loop to optimize its transient response for a given environment. This is the digital equivalent of moving the polesand-zeroes in an analog converter by continuously adjusting the values of resistors and capacitors within its feedback loop, which is practically inconceivable.

#### PMBus™ is a key enabler

The PMBus can be invaluable during product evaluation and development. Here, the board power manager that controls PMBus-compatible devices might be a PC connected to a prototype board via a suitable adapter. Because the physical layer of PMBus relies upon SMBuswhich is a development of I2C-PMBus is generally limited to the board domain, leaving designers free to implement their choice of backplane connectivity. Figure 3 shows the general scheme.

To make development immediately available, Ericsson developed a PC-compatible evaluation kit for 3E products that includes a USBto-PMBus adapter and driver software that substitute for the board power manager. The PC and the kit's application software then assume the role of system host and user interface. This approach provides an extremely fast method for experimenting with parameters such as output voltage settings, power sequencing routines, voltage margining, and fault handling without any need for hardware changes on the board-under-test. When the designer is satisfied with a set-up, the application software can save a configuration file for each 3E device for later use.

While customers can request specific configurations, Ericsson most often delivers 3E parts pre-programmed with a default configuration that reflects a converter's typical application profile. For instance, users can order a point-of-load regulator such as the 20A-rated BMR450 preset to output 1.0, 3.3, 5.0, or 5.5VDC.

It is subsequently possible to reprogram the device to any level from 0.6 to 5.5VDC with 1mV resolution via the PMBus (it's also possible to set the product's output voltage from 0.7 to 5.0VDC in 25 steps with a resistor). As a result, one device covers a range of output voltages, permitting inventory

reductions and easing logistics management. It's also worth noting that the BMR450 and its 40A companion BMR451 can share a common PCB layout, allowing designers to exchange converters as a system's power needs evolve. Similar benefits apply to all 3E family power converters.

If a one-time change of output voltage or any other programmable parameter is all that's necessary, a logical time to do this is at the ATE phase of board manufacture. Alternatively, a distributor may offer a programming service. Assuming a simple end-user application such as upgrading an analog design, it' s possible to dispense with board power management logic on the target board. However, including full PMBus connectivity vastly improves the range of options that are available to powersystem designers. As the PMBus requires just four conductors and a low-cost microcontroller easily accommodates the board power management logic, this approach is well worth considering.

Implementing PMBus connectivity allows the system host to monitor each PMBus-compatible device throughout the equipment' s lifetime. Depending upon the sophistication of the system's supervisory software, this datagathering ability might form the basis for energy cost analysis, rootcause failure analysis, or satisfy other user-specific functions. It may also help avoid system failures. For instance, if the supervisory software detects an unusually high pattern of warning conditions for a particular device, it may signal a service alert to swap out the suspect device before it fails. Similarly, if a power

#### Setting the benchmark for accuracy!

#### **ITxx Current Transducers Series**

Advanced technology for extraordinary performance in accuracy, drifts and response time for unique high-tech industrial applications.

- High precision current measurement: few ppm at +25°C

- Extremely low thermal offset drift from 0.1 to 6.7 ppm/k

- Several current ranges from 12,5 to 24000 A<sub>RMS</sub>

- Really low output noise

- Printed Circuit Board mounting from 12,5 to 60A

- Panel and rack mounting from 60 to 24000 A

- Closed loop Fluxgate technology

- No insertion losses, galvanic isolation

- Any kind of current measurement, DC, AC, mixed...

- Various features provided: Synchronization output, LED and outputs dedicated for normal operation and overload conditions...

www.lem.com

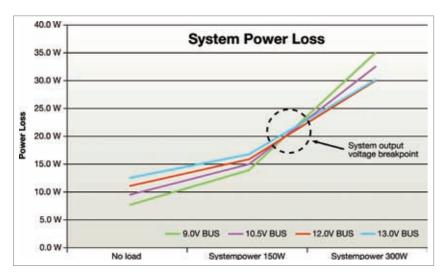

Figure 5: Adjusting advanced bus converter output voltage to payload condition reduces energy consumption

converter's output voltage drifts slightly over time or as a result of wide temperature variations, supervisory software could adjust the device back into full specification.

Another possibility that monitoring a board's power consumption offers is dynamic energy conservation, where supervisory software intelligently varies the output voltage that the intermediate bus converter supplies to the point-of-load regulators. Because virtually all power converters are least efficient at low loads, reprogramming the advanced bus converter from say 12VDC down to 9VDC saves power

dissipation while the point-of-load regulators are running under light load.

When more power is required, supervisory software can seamlessly ramp up the intermediate bus voltage to its optimal level for the new load conditions. Where a pair of power converters operate in a parallel current-sharing arrangement, it will save energy to turn off one if the load level falls within the capability of a single converter. This active approach to power management particularly suits systems that spend significant periods under widely different load conditions.

Figure 6: 3E evaluation kit simplifies learning, testing and programming

#### This is just the beginning

It's important to emphasize that these example scenarios represent just a few of the possibilities 3E power converters with PMBus connectivity make possible, and innovative designers will doubtless find new ones. Also, any of these converters can upgrade analog designs with no special effort on the designer's behalf. They can easily operate stand-alone as they offer analog-style functions such as output voltage adjustment via a single resistor, remote voltage sensing, and single-pin hardware on/off control. The "set-and-forget" capability that PMBus mandates also means that any 3E power converter can be pre-programmed with user-defined parameters that the device then retains for its lifetime or until re-programmed. This makes it possible to finetune a converter for a particular application without requiring PMBus in the target system.

Compared with well-known analog techniques, the downside of digital power conversion is the very substantial amount of R&D effort that's necessary to produce a production-worthy digital converter—which is a prime reason for selecting proven, pre-qualified solutions. To help ease users into the digital power environment, Ericsson offers application engineering assistance and complements its evaluation kit with a large archive of technical papers and application information.

Author: Patrick Le Fèvre Marketing & Communication Director Ericsson Power Modules

www.ericsson.com/powermodules

# **OPTIMIZING POWER MODULES**

#### THE PURSUIT OF INDUSTRY BEST-IN-CLASS PERFORMANCE

#### By Werner Obermaier

In a world where energy efficiency is king, engineers, managers and purchasing departments alike need to examine carefully the route their company takes in the development of new products. It is no longer just a case of going back to the usual module suppliers. Total optimization is now absolutely vital and this can only be achieved cost-effectively with careful forethought and the right module manufacturer.

he market for power modules has proven to be highly successful and has taken a huge load off companies' purchasing and engineering departments by providing a compact, affordable solution which works right first time.

EMI and matching issues are all taken care of with negligible tweaks required. This is a giant leap forward from the traditional method of using discrete components which often required several expensive and time-burning iterations of laborious design to become optimized.

But now the market's requirement is not just for a fast and convenient solution. With the burgeoning adoption of UPS and solar energy sources and the proliferation of so-called solar farms, inverter efficiency takes on a completely new dimension. Every fraction of a percentage-point increase in terms of efficiency and reliability equates to profit. These

systems are installed with the acknowledged expectation that they will run continuously (in the case of UPS) and maintenance-free for a predicted lifetime of up to twenty years. The individual components and topologies selected at the outset, determine the profitability of the operating system. It is a vitally important strategic, purchasing and technical decision to make - and one that cannot be taken lightly. Going back to regular suppliers in the belief that everything is optimized is an assumption that may result in a lost opportunity in the market differentiation of the final product.

Most of the larger companies supplying power modules are constrained in their selection of individual components by corporate edicts and long term alliances, resulting in an adequate, although not necessarily optimum, solution.

With the hugely diverse range of components now available, the

power module designer with no constraints on component selection

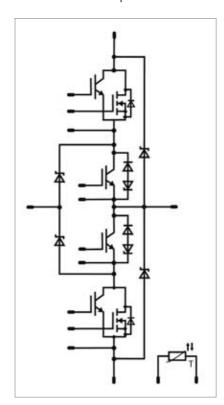

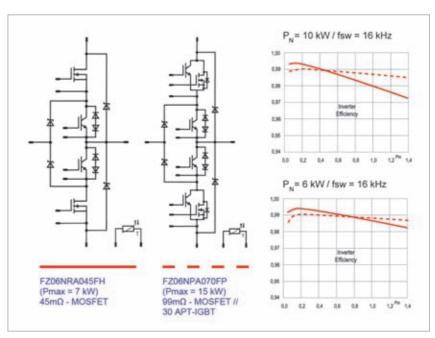

Figure 1: Circuit diagram of flowNPC o module FZo6NPA070FP with parallel switch (combination of MOSFET and IGBT) as outer switch

is the only individual with the ability to truly optimize a system to maximize efficiency, reliability and profit for the end customer. Such scenarios are, however, rare. Working with general suppliers always results in a compromise solution.

Nothing less than the Optimum While in the past a good product which could provide the required performance was good enough, with the globalization of the market and increased competition, this has changed significantly. Companies now have to develop the best possible product to maintain competitiveness. This, in turn, increases the attention to and demands on the individual components used in the product, which is especially true for components providing higher integration levels like power modules.

While power modules have become the standard power component for frequency inverters in industrial drives due to their high reliability, low assembly cost and long usable lifetime -and because of their high load cycle capability in combination with high power capability, this has not been the case in other areas such as solar inverters. The solar inverter market is still driven by the goal to reach the highest possible efficiency. This is normally achieved by using innovative although increasingly complex topologies like HERIC ®, H<sub>5</sub>, NPC, mixed voltage NPC or similar, combined with state of the art semiconductors. In the past this was achieved in most cases by selecting discrete semiconductors from a variety of vendors to achieve the optimum solution. With today' s increased complexity of these circuits, the higher power levels handled and the larger production volumes, the use of a power

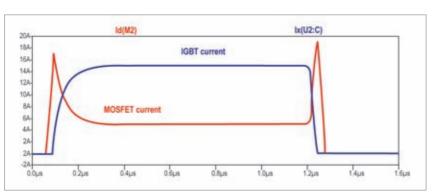

Figure 2: Typical current flow of MOSFET and IGBT in the parallel switch during one switching cycle

module as a subsystem would, in theory, become the obvious next step if it were not for one huge limitation: Most power module manufacturers are at the same time power semiconductor manufacturers making it almost impossible for them to use devices in their power modules from competitors - even where these would be a better, more efficient choice for the targeted application or topology.

Vincotech is in the unique position to focus on power module manufacturing only, which allows the company to choose from the widest range of semiconductor suppliers. This enables the company to provide modules with a completely optimized chip selection. One example of this is the flowNPC o module FZo6NPAo7oFP. Here, a combination of MOSFET and IGBT from different vendors is used to build an optimum product, outperforming both a pure MOSFET and IGBT solution.

Figure 1 shows the circuit diagram of the FZo6NPAo7oFP module which contains the semiconductor for one phase of a 3 phase clamped neutral point inverter. The outer switch is built by a combination of MOSFET and IGBT and is used to generate the high frequency PWM signal. In this arrangement the MOSFET will

be turned on first providing low turn on losses due to its high switching speed, while the IGBT will be turned on afterwards, adding high current low conduction loss capability during the most of the on-time. The turnoff will take place in the opposite sequence; turning off the low speed IGBT first, thus avoiding the normally present tail current with its inherent switching losses. The current waveform for the two devices during one cycle showing the current sharing can be seen in Figure 2.

Most IGBTs used in parallel switch configuration suffer from the effect in that the stored carrier will not recombine during periods where no collector emitter voltage is present, resulting in additional tail current when the MOSFET is turned off, which in-turn results in additional turn-off losses. This can be avoided by using Fairchild's PT-IGBTs as parallel switch.

Figure 3 shows a comparison of module efficiency at different nominal output power levels for the FZo6NPAo7oFP with the parallel switch and the FZo6NRAo45FH with the single MOSFET switch. Both modules are using the same total chip size for the switch. The module with the pure MOSFET switch provides slightly higher efficiency at light load due to the resistive

Figure 3: Comparison of module efficiency for MOSFET and parallel switch based modules at 6 and 10kW output power per phase

characteristic of the MOSFET, while the parallel switch provides higher efficiency over a wide output power

range, resulting in a higher overall efficiency and in turn higher output power capability.

#### Conclusion

Power modules can provide benefits to power electronic equipment such as solar inverter and UPS, especially at higher power levels for more complex circuits and if high reliability levels have to be achieved. For optimum system performance, the combination of a variety of semiconductors, carefully selected from a broad range of semiconductor vendors is required - especially for the upcoming solar inverter market. Vincotech as a specialized power module manufacturer with its wide semiconductor supplier range, is best positioned and equipped to serve and deliver on these requirements.

Author: Werner Obermaier Head of Product Marketing Vincotech GmbH

www.vincotech.com

# **Electrical Engineers (m/f)**

Certainly

ABB is a global leader in power and automation technologies that enable utility and industry customers to improve their performance while lowering environmental impact. ABB operates in more than 100 countries and employs about 117,000 people, whereof 6,400 in Switzerland.

ABB Corporate Research is developing the foundations for the next generation of ABB products in close collaboration with ABB business areas. In Switzerland, the ABB Corporate Research Center is located in Baden-Dättwil in the proximity of Zurich and employs around 200 scientists from more than 25 countries.

In the area of Power Electronics we are looking for high-level electrical engineers (m/f) with strong theoretical skills to join our R&D team.

We offer an inspiring R&D environment, self-determined scientific working in motivated teams with a wide range of experience and competence, the possibility to contribute in emerging R&D areas relevant for future technologies, and excellent opportunities for further

Your tasks: perform applied research in the field of advanced power electronics and integration technologies for industrial components

and systems • contribute to and later acquire and lead R&D projects • conduct research with focus on multi-domain and electromagnetic modeling, simulation, and measurement methodologies • investigate approaches for improving electromagnetic compatibility (EMC) and power density while reducing electromagnetic interferences (EMI)

The requirements: PhD in electrical engineering • deep knowledge of power electronics, electromagnetics, and manufacturing technologies • willingness and ability to learn quickly new scientific areas and broad technical interest • readiness to work in an industrial R&D environment in collaboration with business units • motivation for innovation and independent thinking • fluency in English • strong communication and interpersonal skills

Your contact:

Andrea Kuhn, Recruiting Consultant

Apply online - or find other exciting jobs: www.abb.ch/careers

Power and productivity for a better world™

WWW.POWERSYSTEMSDESIGN.COM WWW.POWERSYSTEMSDESIGN.COM

# THERMOELECTRIC ENERGY

#### HARVESTING AND STORAGE SOLUTIONS

#### By Dave Koester

Advances in distributed sensors and sensor networks have led to an increased interest in renewable and autonomous power sources. The use of waste heat is an attractive source of energy for many applications where power on the order of  $\mu$ W-mW is required.

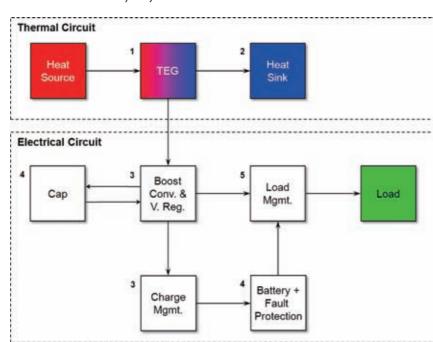

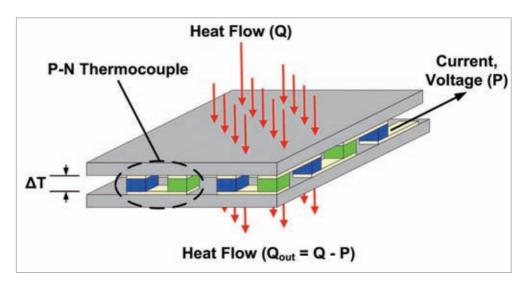

he implementation of a thermoelectric power conversion and energy storage system requires several basic elements in addition to an assumed heat source and electrical load. These elements, shown in schematic form in Figure 1, are: 1) a thermoelectric power generator (TEG), 2) a heat sink, 3) a power conditioning circuit that provides voltage upconversion and regulation, 4) an energy storage device such as capacitor or battery, and 5) a power (load) management circuit. The interaction of these elements is critical to the performance of the system. The following provides further detail about each key element of the system and issues that affect system optimization.

# Thermoelectric Power Generator (TEG)

The direct conversion of heat into electrical energy can be accomplished through the Seebeck effect in which heat flow through a thermoelectric device produces a voltage and current.

The basic building block of any TEG is the PN couple. The PN couple consists of a single element of P-type and N-type thermoelectric material that are connected electrically in series. Heat carries the majority carriers from one junction to the other producing a current and voltage. By placing many PN couples in series electrically and in parallel thermally (see Fig. 2), a TEG can be constructed that generates a voltage proportional to the temperature differential ( $\Delta T$ ) across the elements. The current

Figure 1: The design and optimization of a thermoelectric energy harvesting system is highly dependent on the relationships of these elements

Figure 2: Thermal-toelectric conversion with thermoelectrics. The ΔT across the module is related to the heat flow Q and the thermal conductance

is a function of the number of PN couples.

#### **Heat Rejection**

In order to sustain a  $\Delta T$  across a TEG, there must be heat flow through the device. This requires a heat source and a heat sink capable of rejecting the heat passing through the TEG.

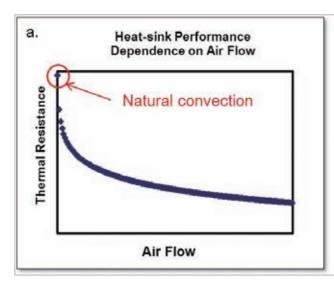

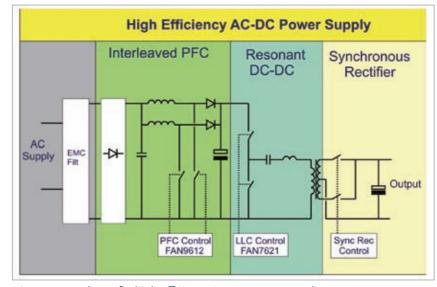

Heat rejection can be accomplished in numerous ways including direct conduction to a large thermal mass, liquid cooling, spray cooling, phase change or simply through convection to the air using a traditional heat sink (the most common and often the lowest cost of these approaches). Heat sinks come in a vast array of sizes, dimensions and materials and choosing the proper one requires a thorough understanding of several key parameters. The parameter describing the ability of a heat sink to dissipate heat is the "thermal resistance,"  $\Theta$ . A low thermal resistance means the sink will do a good job of rejecting heat to the environment while a high thermal resistance will do a poor job. The thermal resistance of any heat sink is affected by the

#### following:

Airflow Speed - The speed of the air flowing across the fins or pins of a heat sink plays a key role in the ability of the sink to dissipate heat to the environment. Even a small amount of air flow across a sink can substantially improve its performance relative to a case with no forced airflow known as natural convection (Fig. 3a). A fan can be used to improve performance but the fan will impact the overall conversion efficiency of the TEG system.

Size, Fin type, Dimension and Spacing - Size and geometry (such as aspect ratio), have a large impact on the performance of a heat sink (Fig. 3b). The optimal fin dimension and spacing depends on the fin material, mode of operation (natural or forced convection) and desired operating condition. Most applications seek to minimize the size of the heat sink. Such optimization requires understanding the operating boundary conditions like temperature and air flow to properly design the size, spacing and number of fins or pins.

Thermal Spreading Resistance

- A large mismatch in footprint

area between the heat source,

TEG and base of the heat sink

can lead to additional thermal

resistance often referred to as

spreading resistance. Performance

can be improved by using a more

thermally conductive material

(such as copper) and/or varying

the base plate thickness of the

heat sink.

Gravitational Orientation - The performance of a heat sink in natural convection mode (i.e., no forced air movement) depends on the orientation of the fins relative to gravitational direction. The dependence of performance on orientation can be reduced somewhat by the use of pin fins rather than plate fins in the heat sink.

### Voltage Regulation and Power Management

In cases where the ambient temperatures and heat flow are not constant, the output of the TEG will fluctuate. These fluctuations must either be tolerated by the load or eliminated by voltage conditioning and/or energy

WWW.POWERSYSTEMSDESIGN.COM WWW.POWERSYSTEMSDESIGN.COM

Figure 3: The performance of the heat sink is dependent on (a) the air flow with the special case being no air flow (natural convection) and (b) size

storage. Because the voltage output of a TEG is proportional to the temperature differential  $\Delta T$ across the TEG, if the  $\Delta T$  is small, it may be necessary to boost the voltage to the minimum usable value.

Boost Converters (>400mV) - Many of today's electronics require a minimum of 1.8V to 3V to operate but the heat source and TEG combination may be unable to generate such a voltage. Fortunately, there are numerous commercially available boost converters that can convert voltage from as low as 400mV to greater than 3V.

Micro-Power Up-Converters (>30mV) - Recent advancements in up-conversion now make it possible to up-convert voltages as low as 30 mV. This is particularly important in cases where the  $\Delta T$ available from the heat sources is very low. One example of this is generating power from the human body were reasonable and achievable  $\Delta Ts$  are in the range of only 5-10K.

#### **Energy Storage**

Energy storage is needed when continued operation of the load is required while thermal energy is unavailable. Two general types of storage are used that offer differing characteristics. (1) Batteries (cells) provide high energy storage density but since the energy is stored chemically, the discharge rate is slow. The term "power density" is used to describe the limits on energy discharge. The other type of storage device is the capacitor. (2) Capacitors store energy physically by charging plates that can be quickly discharged. While the energy storage density of capacitors is smaller than batteries/cells, they have high discharge rates or power density making them ideal for quick bursts of power.

Systems will sometimes contain both types of storage especially if the load includes transient high-power devices such as a transmitter. Capacitors do not need any special circuitry to function well but batteries

typically do. Charge management devices increase the lifetime of the battery or cell and are available from several manufacturers. They also aid in the performance of the system by allowing charging only when there is sufficient power available, in excess of what load requires.

#### **Power Management**

Lastly, power (load) management circuits switch the load between the boost convertor and the battery thereby isolating the cell from the output of the boost convertor. This benefits the cell by removing the drain and allowing it to charge when power is available directly from the boost convertor. This also minimizes the risk of a faulty or exhausted cell from shunting the output.

Author: Dave Koester Vice President of Engineering Nextreme Thermal Solutions

www.nextreme.com

# POWER EFFICIENCY BREAKTHROUGH

#### SYNCHRONOUS RECTIFICATION OF AN LLC OUTPUT

#### By John Stephens

POWER SUPPLIES

With demand for high efficiency becoming part of product specification across the whole load range, design engineers are reviewing AC-DC power supply topologies with the specific aim of reducing power loss.

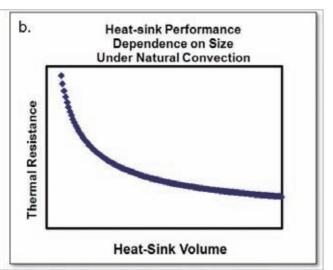

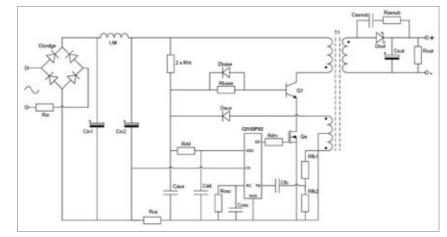

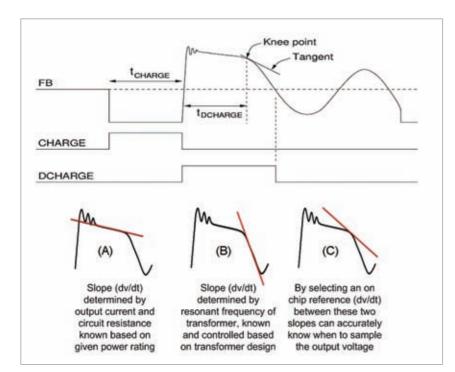

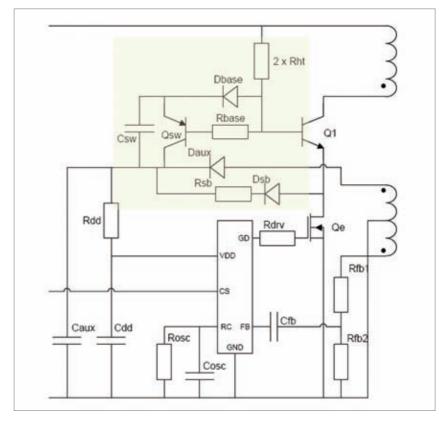

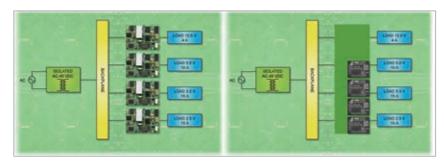

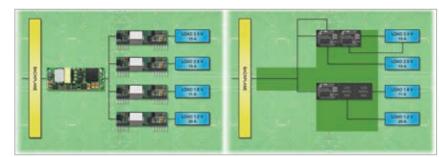

ne such topology offering class-leading efficiency is illustra ted in Figure 1. This article examines claims by IC manufacturers to have dealt with the last remaining large source of power losses in this topology: the output rectification stage.

Previous enhancements to this topology have produced improved Power Factor Correction (PFC) control ICs for the interleaved Boundary Conduction Mode (BCM) stage, and new LLC control ICs which enable more efficient designs.

So now losses in the output rectification stage of the LLC resonant converter tend to dominate the power losses budget. To make the next step forward in efficiency, synchronous rectification is required.

Two newly introduced ICs, from International Rectifier and Diodes Inc, are now being promoted as potential solutions to the problem.

Before these devices reached the market, synchronous rectification for LLC resonant converters could not practically be implemented because of the complexity and difficulty of the technique.

The reality of synchronous rectification in resonant LLC circuits For voltage-fed circuits, typical of the Pulse Width Modulation (PWM) or series-parallel resonant topologies, additional windings or tapping

from the power transformer would suffice for driving the synchronous rectification circuits.

The LLC resonant topology is different: since it is a currentfed, capacitor-loaded structure, it cannot use the power transformer waveforms to drive synchronous rectification circuits. This is because the voltage on the secondary windings is connected to the output via the mosfet during its conduction

Figure 1: Topology of a high-efficiency AC-DC power supply

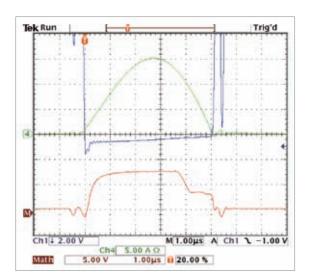

Figure 2:  $I_{ds}$ ,  $V_{ds}$  and  $V_{g}$  100% F.L. in ZXDG3103 circuit

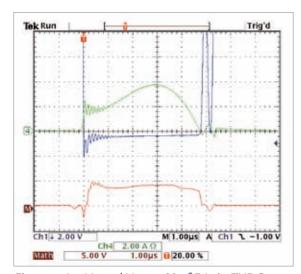

Figure 3:  $I_{ds}$ ,  $V_{ds}$  and  $V_{g}$  at 25% of F.L. in ZXDG3103 circuit

time, and therefore holds the winding voltage until the mosfet switches off.

One method of resolving the problem is to sense the current flow and voltage around the mosfet. This requires the following functions:

- Current sensing (of I<sub>ds</sub>)

- Voltage sensing (of V<sub>ds</sub>)

- High-speed logic

- High-current gate drive

These sensing functions, and the use of their measurements, would

be extremely difficult to implement in discrete components. Fortunately, two new ICs do the job for the design engineer: the ZXGD3103 from Diodes Inc, and International Rectifier's IR1168.

Both are secondary side drivers operating closely with the mosfet that replaces the Schottky diode. The ZXGD3103 is a single driver requiring two ICs, whereas the IR1168 is a dual driver requiring only one IC. Both sense the current by virtue of the drop in Vds at the mosfet, but their internal workings are different. (More details on the operation of these devices are available at www.diodes.com, and in Application Note AN-1139 on www.irf.com.)

#### The test circuits

To assess the extent to which these secondary side drivers can deliver power savings in the output rectification stage of LLC power supplies, a test set-up was devised based on an evaluation board developed by Fairchild Semiconductor. This is a 390Vdc input to 25Vdc output resonant LLC power supply capable of supplying 200W into a load.

To simplify the test set-up, only one half of the IR1168 – a dual driver IC -

was used.

Figure 2 details the waveforms at full load (F.L.) and Figure 3 details the waveforms at 25% of F.L.

Ch1 =  $V_{ds}$  inverted

Ch4 =  $I_{ds}$  flowing to Co

Maths -  $V_{gs}$  (Ch2-Ch3) (where Ch2 -  $V_{dg}$  and Ch3 -  $V_{ds}$ )

It is interesting to see in both diagrams the fast gate drive voltage. In ~200ns after detection of the parasitic diode forward volt drop within the MOSFET, Q1 turns on, reducing its voltage ( $Ch1 - V_{ds}$ ).

In both tests,  $Q_1 V_{ds}$  is higher than expected. This may be due to the circuit inductance and to the capabilities of the oscilloscope.

At full load, the gate drive voltage reduces as the sinusoidal current starts reducing. This is probably due to the inductance of the circuit and the inductance of the Q1 TO220 package. Improved layout and selection of a lower inductance packaging should resolve the issue.

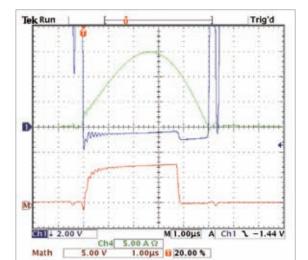

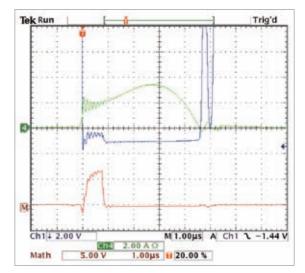

As before, Figure 4 details the waveforms at F.L. and Figure 5 details the waveforms at 25% of F.L. for the test circuit using the IR1168 device.

Like the ZXGD3103, the IR1168 test circuits reveal a fast gate drive voltage – in <200ns after detection of the parasitic diode forward voltage drop within the mosfet, Q1 turns on, reducing its voltage (Ch1 –  $V_{ds}$ ).

As before, Q1 Vds is higher than expected, probably for the same reasons.

In the full-load test circuit, the early termination of the gate drive

voltage (Vgs) as the sinusoidal current starts reducing is probably due to the inductance of the circuit and the inductance of the Q1 TO220 package. As in the previous test circuit using the ZXGD3103, improved layout, reduction of resistances and selection of a lower inductance packaging should resolve the issue.

# So how much power does implementation of synchronous rectification save?

The key reason for implementing synchronous rectification is to save power. The tables below detail the key parameters of interest.

With improved layout and mosfet package selection, both synchronous rectification circuits could exhibit even higher efficiency; the small differences in efficiency between the ZXGD3103 and IR1168 circuits shown in the tables are therefore not material.

What is clear is that substantial power savings are possible by implementing circuits that can be designed with little trouble by following the manufacturers' application guidelines.

What is also clear is that the threshold at which a power saving can be observed appears to be at

around 25% of F.L. and above.

At full load the Schottky diodes warm up the heat sink to the extent that a small fan is required for continuous operation. By contrast, the mosfet in the synchronous rectifier circuits can be operated at full load without a heat sink, and indeed in both cases was cool to the touch. This points to the possibility of a billof-materials savings to be made from the elimination of heat sinks and fans.

In conclusion, with the introduction of the ZXGD3103 and IR1168, the implementation of synchronous rectification of the circuit output stage of LLC circuits has become a practical

possibility. This new technique appears to deliver power savings anywhere from 25% of full load up

Figure 4:  $I_{ds}$ ,  $V_{ds}$  and  $V_{g}$  at full load in IR1168 circuit

Figure 5:  $I_{ds}$ ,  $V_{ds}$  and  $V_{g}$  at 25% of full load in IR1168 circuit

to 100% of full load.

For more information on implementing high-efficiency power supplies, contact any branch of Future Electronics. The ZXGD3103 and IR1168 parts mentioned in this article are available to buy from Future Electronics.

Author: By John Stephens Technical Project Manager, European System Design Centre Future Electronics

www.futureelectronics.com

|                 |    | Schottky<br>Diodes | ZXDG3103+IRFB4110 | IR1168+IRFB4110 |

|-----------------|----|--------------------|-------------------|-----------------|

| Losses          | W  | 13.52              | 8.85              | 9.73            |

| Efficiency      | 96 | 93.7               | 95.8              | 95.4            |

| Power<br>Saving | W  | reference          | 4.67              | 3.80            |

Table 1: power dissipation at 25% of F.L. (50W)

|                 |   | Schottky<br>Diodes | ZDG3103+IRFB4110 | IR1168+IRFB4110 |

|-----------------|---|--------------------|------------------|-----------------|

| Losses          | W | 5.91               | 5.16             | 5.78            |

| Efficiency      | % | 89.4               | 90.6             | 89.6            |

| Power<br>Saving | W | reference          | 0.74             | 0.13            |

Table 2: power dissipation at F.L. (200W)

# DESIGNER'S PERSPECTIVE

#### SEMICONDUCTOR LIFECYCLE MANAGEMENT

By Eric Marcelot

It is estimated that 3% of the global pool of electronic components is made obsolete each month, and on a long term defence project, typically 50-70% of the semiconductor products incorporated are made obsolete before the program is even commissioned.

his is a very sobering thought for any designer settling down to spec a new system, especially so if they are working on a military or aerospace project that may take many years to delivery and then be expected to be in service for 10s of years thereafter.

This isn't just a hypothetical scare story, it is being played out now. A case in point is the B-52 bomber, which e2v aerospace and defense Inc (previously QP Semiconductor) ships parts for on a weekly basis. This platform has been in service for over half a century and is likely to continue to be in operation for at least another 30 years. This means that a project that was initially supposed to have a 30-50 year life cycle will have exceeded 80 years by the time it is grounded.

It is therefore vital that a new approach is taken to managing and mitigating against the effects of Semiconductor obsolescence, an approach which can help with the platforms and systems being

Wafer storage facility in Santa Clara CA

developed today as well as those already in service.

#### So what is being done to help?

ezv recently entered an agreement with Freescale Semiconductor to extend the useful life of 68K-series microprocessors for the military, aerospace, commercial, and industrial markets. ezv will wafer bank die based on advised customer requirements to ensure the continued supply of the devices following the discontinuance of the products by Freescale.

Programmable Logic Device (CPLD), from Santa Clara CA facility, used in high reliability aircraft requirements, and supplied in support of long term programs

Once Freescale ceases production of the 68020, 68882, and 68C000 processors, e2v's portfolio of high-reliability grade products will be extended with commercial-grade versions in both plastic and ceramic packages. Based on up front forecast requirements, the Freescale products will remain available from e2v for the next 10 years, or longer. In fact, Freescale has licensed the company to deliver high-reliability versions of its products for more than 25 years.

The Freescale licence arrangement means that e2v will build and sell its own products, from the 68K family to high-performance Power Architecture devices, by sourcing commercial wafers and devices from Freescale and then repackaging, screening, characterizing, and testing at extended temperatures for military and aerospace requirements.

In April, e2v aerospace and defense

also released re-engineered versions of the QP Semi QP741 and QP747 operational amplifiers, manufactured on a bipolar process to serve as drop-in replacements for the National/Fairchild LM741 used in key military/aerospace applications. (Market forecasts indicate that inventories of these military grade devices will be depleted in the near term.) Essentially, the company is extending its product range for a wider set of applications, where system redesign is complex and expensive.