SPECIAL REPORT: WHITE GOODS (PG 41)

April 2011

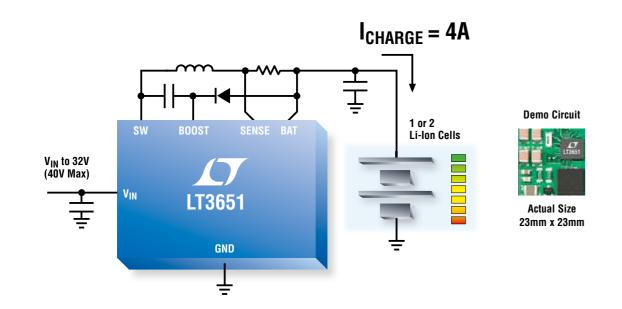

## Charge **BIG** Batteries Fast

### High Voltage, High Current, High Efficiency Charger

The LT<sup>\*</sup>3651 enables fast charging of Li-Ion/Polymer batteries by delivering up to 4A of continuous charge current with minimal power loss. This is due to its high efficiency switchmode topology, including on-chip synchronous MOSFETs. Its autonomous operation means no microcontroller is necessary and the device integrates an onboard C/10 or timer charge termination. The LT3651's programmable input current limit with PowerPath<sup>™</sup> control regulates charge current to maintain a constant supply current, preventing the input supply from collapsing.

#### **V** Features

- Charge Current up to 4A

- Wide Input Voltage Range: 4.8V to 32V (40V Max)

- Programmable Switching Frequency: 200kHz to 1MHz

- C/10 or Timer Onboard Charge Termination

- High Efficiency Operation Minimizes Power Loss

- Programmable Input Current Limit

- Compact 5mm x 6mm QFN Package

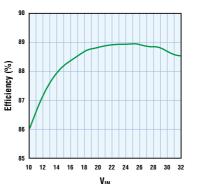

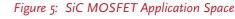

#### Efficiency vs VIN

### Info & Free Samples

**D**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of tive owners

Europe Sales offices: France 33-1-41079555 Italy 39-02-38093656 Germany 49-89-9624550 Sweden 46-8-623-1600 UK 44-1628-477066 Finland 358-9-88733699 Distributors: Belguin ACAL 32-0-7-2005983 Finland Tech Data 358-9-88733382 France Arrow Electronique 33-1-49-784978, Tekelec Airtronic 33-1-56302425 Germany Insight 49-89-611080,

Setron 49-531-80980 Ireland MEMEC 353-61-411842 Israel Avnet Components 972-9-778-0351 Italy Silverstar 39-02-66125-1 Netherlands ACAL 31-0402502602 Spain Arrow 34-91-304-3040 Turkey Arrow Elektronis 49-02-16-465090 UK Arrow Electronics 44-1234-791719, Insight Memec 44-1296-330061

## THE INDUSTRY'S BROADEST PRODUCT SELECTION AVAILABLE FOR IMMEDIATE DELIVERY

### 490,000+ PRODUCTS IN STOCK **470+ SUPPLIER PARTNERS NEW PRODUCTS ADDED DAILY**

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an autho distributor for all supplier partners. New product added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

The industry's broadest product selection available for immediate delivery

Find contact and ordering information for your region at www.diaikev.com/europe

f 🖻 🛎 🔄 GET CONNECTED

### CONCEPTINTELLIGENT POWER ELECTRONICS

### 2SP0115T Gate Driver

Unleash the full power of your converter design using the new 2SP0115T Plug-and-Play driver. With its direct paralleling capability, the scalability of your design into highest power ratings is unlimited. Rugged SCALE-2 technology enables the complete driver functionality on a single PCB board, exactly fitting the size of 17mm dual modules.

Combined with the CONCEPT advanced active clamping function, the electrical performance of the IGBT can be fully exploited while keeping the SOA of the IGBT. Needless to say that the high integration level provides the best possible reliability by a minimzed number of components.

### Features

Plug-and-Play solution 1W output power 15A gate current <100ns delay time ± 4ns jitter Advanced active clamping Direct- and halfbridge mode Direct paralleling capability 2-level and multilevel topologies DIC-20 electrical interface Safe isolation to EN50178 UL compliant 50.- USD @ 1000 pieces

P SD Power Systems Design: Empowering Global Innovation

#### WWW.POWERSYSTEMSDESIGN.COM

Visit us online for exclusive content; Industry News, Products, Reviews, and full PSD archives and back issues

#### VIEWpoint

White Goods and Woes By Cliff Keys Editorial Director & Editor-in-Chief, Power Systems Design

**POWER**line IR's New Family of PFC ICs

**POWER**player

White & Consumer Goods, Bv Cliff Kevs. Editorial Director & Editor-in-Chief, Power Systems Design

MARKETwatch

Energy Conservation Efforts Drive Appliance Innovation, By Elizabeth Cruz, IMS Research

**DESIGN**tips Power Supply Development Part XII By Dr. Ray Ridley, Ridley Engineering

#### COVER STORY

**TECHNICAL FEATURES**

### <sup>23</sup> Digital Power

Digital POL Improves Key Metrics By Patrick Le Fèvre, Ericsson Power Modules

### SMD Cube Skrinks Footprint By Ann-Marie Bayliss,

Murata Power Solutions

Automotive Electronics

Direct Fuel Injection By Don Zaremba, ON Semiconductor

### 34 Power Management

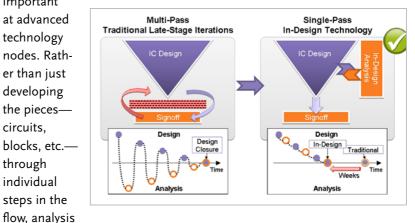

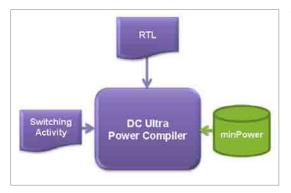

Pain Management in Power Optimization By Cary Chin, Synopsys

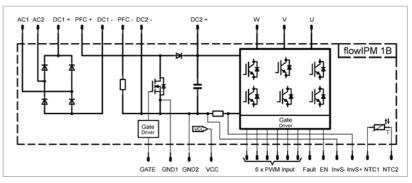

#### 37 Power Modules

Increasing Efficiency By Mark Steinmetz Vincotech GmbH

#### SPECIAL REPORT: White Goods

### 42 Cost Cometitive SiC

By Bob Callanan, SiC Power Products Cree Inc.

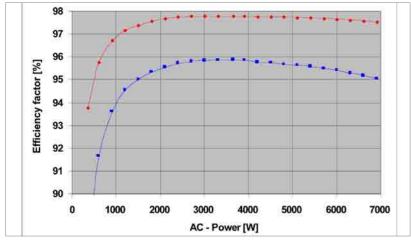

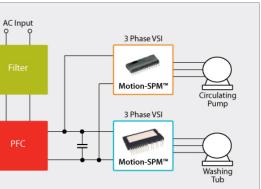

### 45 White Goods Technology

By Dr. Stephan Chmielus, FairChild Semiconductor

### 47 Automated Control

By Randy Skinner, Lattice Semiconductor

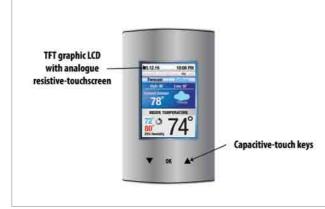

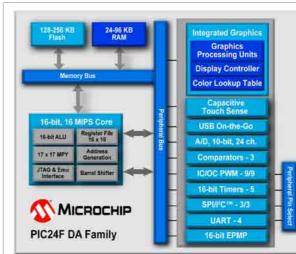

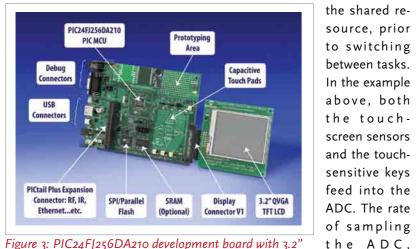

#### Integration In Embedded HMI

By Rishi Vasuki, Microchip Technology

#### POWER SYSTEMS DESIGN APRIL 2011

#### 57 Reliability In White Goods

By Graeme Clark, Renesas Electronics Europe

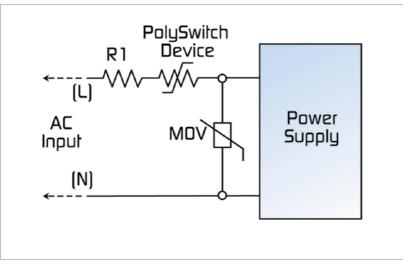

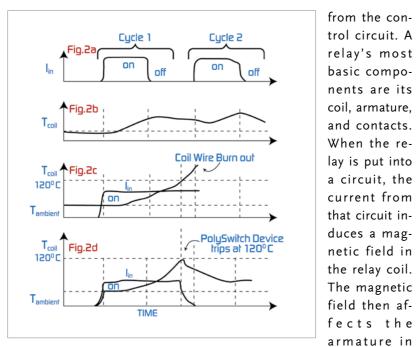

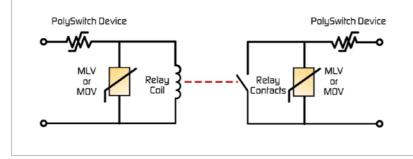

#### Circuit Protection Considerations

By Barry Brents and Matt William, TE - Circuit Protection

#### CAREERdevelopment

Digital Power Control Impacts Power Design on Many Levels,

By David G. Morrison, Editor, How2Power.com

#### GREENpage

Domestic Efficiency Reported By Cliff Keys, Editor-in-Chief, PSDE

Dilbert

WWW.POWERSYSTEMSDESIGN.COM

AGS Media Group 146 Charles Street Annapolis, MD 21401 USATel +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### Editor-in-Chief Cliff Kevs cliff.keys@powersystemsdesign.com

#### **Contributing Editors**

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering rridley@ridleyengineerng.com

David Morrison, How2Power david@how2power.com

#### **Publishing Director**

Jim Graham jim.graham@powersystemsdesign.com

#### Publisher

Iulia Stocks julia.stocks@powersystemsdesign.com

#### **Circulation Management**

Kathryn Philips kathryn.phillips@powersystemsdesign.com

**Research Director**

Meghan Corneal meghan.corneal@powersystemsdesign.com

Magazine Design

Louis C. Geiger louis@agencyofrecord.com

#### **Production Manager**

Chris Corneal chris.corneal@powersystemsdesign.com

Registration of copyright: January 2004 ISSN number: 1613-6365

AGS Media Group and Power Systems Design Europe magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or ommissions in the material contained herein regardless of whether such errors result from negligence, accident or any other cause whatsoever. Send address changes to: circulation@powersystemsdesign.comFree Magazine Subscriptions

go to: www.powersystemsdesign.com

Volume 8, Issue 2

## WHITE GOODS **AND WOES**

Welcome to this issue of PSD where we carry a feature section on white goods and domestic appliances. In former times these devices had no regard for energy efficiency or, in the case of motorized appliances, the noise they generated. These days are fast coming to an end. Regulations are ever tightening and consumers themselves are now becoming more concerned with the energy they consume - both from a cost and from an environmental standpoint. This is driving manufacturers of these appliances to demand better methods of power and motor control which, in turn, normally requires more sophisticated power and control management in the development of modern, consumer-friendly products.

For the world's semiconductor suppliers, after six consecutive quarters of sequential growth, the fourth quarter of 2010 saw revenue contract by 3.7% over the previous period—the first quarterly retreat since the beginning of 2009-according to new research from IHS iSuppli. Revenues for the 298 semiconductor suppliers tracked by the IHS iSuppli Competitive Landscaping Tool (CLT) fell to \$77.2 billion in the fourth quarter of 2010, down from \$80.1 billion in the earlier quarter. But this depressed revenue was still 11.9% higher than the fourth quarter of 2009. Despite the fourth-quarter contraction, semiconductor revenues surged by \$74.5 billion in 2010, setting a new record and surpassing the prior record increase during the dot-com bubble of 2000.

Apple fans are no-doubt aware that the company has managed to significantly reduce the thickness and weight of the iPad 2 by trimming the dimensions of several key components, most notably the battery, a teardown analysis by IHS iSuppli has revealed. This reduction in thickness of the battery subsystem is due to Apple moving from two thicker cells to three thinner ones, flattening out the entire battery structure.

This refinement to the design spurred a 10-15% increase in its iPad 2 power-density, which is a measure of battery life relative to the mass of the battery. It shrinks the iPad 2's weight by 5 grams, while still delivering the same battery lifetime.

The absolute horror of the earthquake in Japan, already well reported, certainly will continue to cause disruption to the global electronics market and has the potential to greatly impact the whole technology industry. We wish the people of that great nation well and will leave the daily reports to those best qualified.

I hope you enjoy our new look and especially our new, user-designed website which is updated on a real-time basis. Check out the community section, naturally after our fun strip, Dilbert, at the back of the magazine. Thank you for your extremely helpful feedback, and please keep it coming.

All the best,

#### Cliff

Editorial Director & Editor-in-Chief Power System Design Cliff.Keys@powersystemsdesign.com

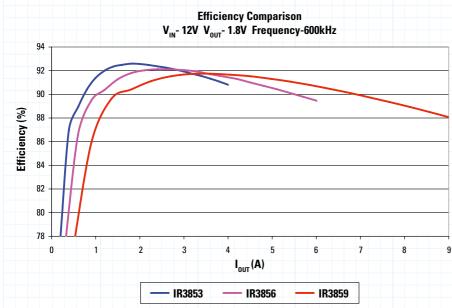

## **IR'S NEW FAMILY OF PFC ICs**

International Rectifier, has introduced the IR115x family of µPFC<sup>™</sup> power factor correction (PFC) ICs for a wide variety of AC-DC applications including lighting, LCD/PDP TV and game consoles, fans, air conditioners, uninterruptible power supplies (UPS) and Switch Mode Power Supplies (SMPS), ranging from 300W to 8kW.

he IR115x ICs, utilizing IR's One Cycle Control (OCC) technology,

offer high power factor (PF), low total harmonic distortion (THD) and excellent DC Bus regulation while enabling drastic reduction in component count, PCB area and design time compared to traditional solutions. The ICs are designed to operate in continuous conduction mode Boost PFC

converters with average current mode control over 85-264VAC input line voltage range.

By integrating more features than traditional PFC solutions and eliminating the need for external implementation, the IR115x significantly reduces the overall cost and complexity of a feature-rich PFC control design compared to traditional PFC

solutions while offering enhanced protection and safety.

The new µPFC<sup>™</sup> ICs offer advanced system-enabling and protective features including dedicated pin for over-voltage protection, cycle by cycle peak current limitation, open loop protection, VCC UVLO and programmable soft-start. The user initiated micropower startup/sleep-mode enables compliance with standby power requirements mandated by regulations such as Energy Star, Green Power and Blue Angel. The IR1152S and IR1153S also feature brown-out protection.

The IR1155S offers programmable switching frequency between 48 kHz to 200 kHz based on the specific application requirement, while the IR1153S offer fixed

The devices are lead free and RoHS compliant. Datasheets, overviews application notes and online design tools are available on the International Rectifier website. The IRAC1152-350W and IRAC1155-300W reference designs, demonstrating the design of a universal input 350W AC-DC Boost PFC Converter, are also available. Design & layout tips are included.

#### www.irf.com

100kHz.

## WHITE & CONSUMER GOODS

Reported By Cliff Keys

With these goods becoming more energy efficient as a function of regulations and consumer demand coupled with the need to

add more functionality, manufacturers are hard-pressed to differentiate their products and in finding the space to pack it all in. I talked with Wisam Moussa, Global lead of FAE for Murata Power Solutions.

aturally, there are sophisticated chips around that can control the motorized parts of today's domestic appliances and there are many solutions around to do this. The area often neglected, or at least left to the last phase of development, is the heart of any system; the power supply. This phase of the product design is not so simple. It must take up the smallest space, be highly efficient and completely reliable under a variety of often harsh environments. On top of this is the need to consider safety and isolation. All these features add to the cost, but these days manufacturers who want to deliver a high quality product, with a reliable and long maintenancefree life are willing to make this investment. Apart from the

performance enhancement, the reputation of the manufacturer can then enter the realms of a 'quality brand'.

Designing a tiny DC/DC converter that meets these performance expectations and that provides a degree of future-proofing is not straightforward. The first challenge is to select a topology that meets the size constraints that miniaturisation demands, yet is capable of adequate output power delivery, isolation and regulation. The chosen approach should be able to address a range of common input and output voltages as well as ideally being extensible to deliver more power from a similar platform.

Power engineers are under constant stress to deliver on time and 'right first time' to meet market entry deadlines. Often with little time to tweak and finetune a circuit, the safest solution. and the most cost-effective when considering the potential cost of redesign or spins is to choose a fully optimized module that is virtually guaranteed to work first time.

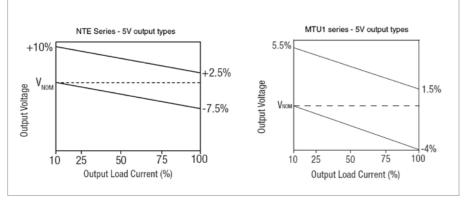

Power manufacturers, by combining proprietary circuit enhancements and recent component fabrication techniques, can improve the load regulation of a converter. For example, Murata Power Solutions' engineers were able to increase their MTU1 part's load regulation performance to a maximum -4, +5.5% from 10% of full load upwards. By comparison, previous ranges achieved -7.5, +10%. For many applications,

the load regulation these enhancements offer obviates the need for inefficient and spacehungry linear post-regulation stages.

These efficiency improvements translate into an approximately 56% reduction in internal power dissipation that reduces internal hot-spots maximising reliability while minimising the heat load that the host equipment has to accommodate. The MTU1 series requires no derating over its -40 to +85°C operating range. Also the reduced capacitance further isolates input and output, making the part far less

Email: sales.caps@nwl.com

susceptible to transmitting noise through its isolation barrier which could potentially disturb sensitive loads.

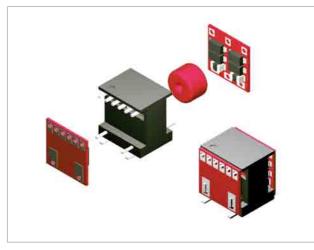

But the most dramatic improvement that the MTU1 series introduces is the part's new footprint, which shrinks the 12.70 x 11.70mm pad land pattern that industry-standard parts use to just 9.10 x 6.08mm. This represents a footprint area over the new device's pins of 0.69 cm2 and an effective power density of 1.71W/cm3 for a cubelike outline that measures 8.2 x 8.4 x 8.5mm.

- Compact, economical design

- Rugged, reliable, and robust

- Reduce installation time by 75%

#### POWER SYSTEMS DESIGN APRIL 2011

Significantly - and unlike some plastic-encapsulated packages that industry-standard components employ - the MTU1's composite assembly has a level 1 rating for moisture sensitivity (MSL1).

The power engineer's job is not an easy one. By utilizing this technology, especially in the example of white and consumer goods used here, designers can avoid the problems that plague many manufacturers' brands further down the line.

www.murata-ps.com

## **ENERGY CONSERVATION EFFORTS DRIVE APPLIANCE** INNOVATION

#### By Elizabeth Cruz

As the price of energy continues to rise, regulatory bodies around the world are continuously looking for new ways to reduce electricity consumption. New and tougher energy efficiency regulations are being

introduced and these offer interesting opportunities for new technologies in home appliances.

he EU's Energy Label has added three classes on top of the previous highest efficiency band; China continues to push minimum energy requirements for room airconditioners and cold appliances, and the US's Energy Star program is driving major reductions in energy use for most appliance types. These more stringent standards are helping to stimulate design changes in a traditionally conservative market.

In Europe, over 90% of appliances sold are in the "A" class of the EU Energy Label scheme, which tells consumers how efficient an appliance is and therefore how much can be saved on their electric bills. In 2010, the

EU approved three new energy classes beyond "A" that will go into effect for washing machines and dishwashers, which must also include noise declarations for these appliances. Additional regulations from the EU, under the Ecodesign Directive, are aimed at limiting stand-by and off-mode power losses. By 2013, certain appliances will be required to use less than 0.5 watts of energy in offmode, affecting the design of user interfaces, auxiliary power supplies and input filters.

The growth of a middle-class in China has been accompanied by a major increase in ownership of home appliances and in residential electricity use. In 2010 the National Development and

Reform Commission of China (NDRC) increased the minimum energy efficiency requirements for room air conditioners by 23% from the previous standard. R oom air conditioners, which account for roughly one-fifth of energy demand in China, are becoming more efficient by using inverter-based variable speed drives to control the compressor and sometimes also the motor running the fans in the unit. The regulation is aimed at saving around 636 billion kilowatt hours of electricity annually.

The US is also raising energy efficiency standards as the potential for energy savings through technology increases. Proposed changes to the Energy Star program (slated to take effect

in 2014/2015) will call for a reduction of energy use in refrigerators and freezers by 30%, clothes washer efficiency increases of 26% to 43% for top and front loading respectively, and room air conditioner efficiency increases of up to a 15%. By 2013 dishwasher manufacturers will be called to increase efficiency by 14% and reduce water consumption by 23%. The introduction of more accurate pressure sensor technology, capable of measuring water levels in the drum to an accuracy of less than 1 millimeter, is an effective tool in reducing unnecessary water use.

The above examples of tightening regional energy standards underline the potential for innovations in electronics design in white goods. The appliance industry has traditionally been slow to adopt new technology, but with growing demands on appliance makers to reduce energy consumption, this is changing. New technologies and uses for motor control, power supplies, sensors and more will increasingly have a place in major home appliances.

Advanced motor control is now advancing aggressively in some appliance types such as room air conditioners and dishwashers. Further increases in adoption are foreseen in the next five years, particularly in washing machines and refrigeration. Together with greater innovation in the design of user interfaces, these trends will maintain the interest of semiconductor and component companies in the home appliance market over the next five years.

Author: Elizabeth Cruz Market Analyst, Power & Energy-Appliances IMS Research

www.imsresearch.com

### efficiency solutions by direct bond copper

17 - 19 May, Exhibiton Centre Nuremberg Visit us in Hall 12, Stand 310 PCIM Europe 2011

> **High thermal** conductivity **Excellent for chip** on board **Optimized heat spreading**

> > DBC SUBSTRATE

**Highly integrated** cooler **Outstanding thermal** performance Customized design

DBC COOLER

curamik electronics GmbH Am Stadtwald 2 D-92676 Eschenbach Phone +49 9645 9222 0 info@curamik.com www.curamik.com

A division of

## POWER SUPPLY **DEVELOPMENT DIARY**

### Part XII

#### By Dr. Ray Ridley

This article continues the series in which Dr. Ridley documents the processes involved in taking a power supply from the initial design

to the full-power prototype. Parts X and XI of this series of articles presented the first seven rules for good PC board layout. Part XII finishes up the design rules for good PCB layout design, focusing on the judicious use of planes.

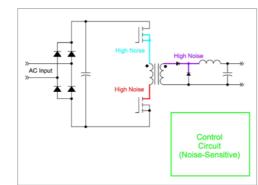

**CB Layout Rule 8: Use** Planes to Capture Noise Switching power supplies generate high-frequency waveforms with both high-frequency and highamplitude current and voltage pulses. In the last article of this series, it was shown how to keep current loops small in order to minimize leakage inductance and magnetic EMI generation. This is an essential step since shielding of magnetically-generated noise is difficult. It is better not to generate it in the first place, hence the need to close the highfrequency current loops. Noise is also generated by electrostatic antennae created by the power supply components.

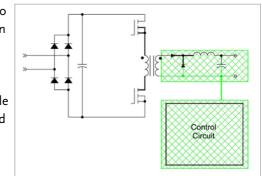

coupled with large-area components or heatsinks, will generate considerable amounts of EMI. Figure 1 shows the basic schematic of the forward converter with a single output. The worst electrostatic noise generators are shown in blue, red, and purple. These are the nodes of

the circuit with the highest dv/ dt waveforms. Typically, the waveform shown in red is the worst offender since it is tied to the large surface area of the drain of the lower power FET.

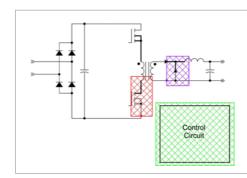

Shielding planes can be used to greatly reduce the effect of these noise-generating nodes. Three such planes are shown in Figure 2.

Figure 1: Forward Converter Schematic showing Electrostatic Noise Generators

These can be implemented in the PC board, if space and available layers allows, and if the power components are surface mounted. The planes should be tied to local RF ground points, such as the return of the main power rail on the input, or the return of the output voltage. Notice that there is no plane for

Figure 2: Shields for Collection of Electrostatic

Circuit Shielding (Green). Colored Dots Show

Noise (Red and Purple) and for Control

Where Shields are Connected.

this is normally self-shielding

due to the layout of the power

packages. The substrate of most

FETs are connected to the drain

connected to an RF ground point

on the positive side of the input

of the FET. The upper FET is

If the power components are

through-hole mounted, the use of

planes to collect EMI in the PCB

case, the heatsinks of the power

components themselves should

from the power devices.

Shield from Noise

Layout Rule 9: Use Planes to

PWM controllers can be very

sensitive to noise, and must

be protected to ensure proper

operation. Stray noise into the

ports of high-gain operational

amplifiers and comparators can

lead to catastrophic failures of

act of applying an oscilloscope

power supplies. Even the simple

be locally grounded, ensuring that

they have suitable voltage isolation

will be of limited value. In this

rail.

the source of the upper FET since

probe improperly to a control circuit can result in failure of a switching power supply.

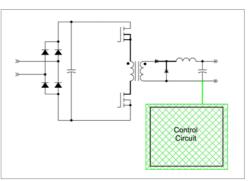

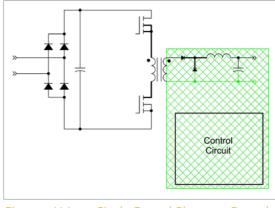

It is highly advisable to provide a ground plane underneath the area of the control chip and its surrounding components. This will establish a

low-impedance ground connection to all parts of the control circuit, and minimize any EMI pickup loops and stray inductance that may cause problems. The ground plane used to shield the control circuit should be tied properly to the return of the main output if this is referred to the same ground. A single connection should be provided to connect the two common points as shown in Figure 3.

Figure 3: Tying the Ground Plane to a Single Point on the Main Output

If extra layers are available on the PCB, it can be tempting to pour a ground plane over much larger areas in order to reduce noise. However this can have the effect of degrading the integrity of the

Nodes which have high-frequency

voltage waveforms, when

Figure 5: Two Separate Ground Planes Achieve Noise Shielding and Proper Ground Integrity

ground in the quiet areas of the circuit. For example, if a ground plane is placed on the PCB as shown in Figure 4, noise problems can result. The high-frequency pulsating currents in the secondary will flow through parts of the ground plane, and this can disturb noise-sensitive components.

A better layout for ground planes is illustrated in Figure 5. The upper part of the plane is used

for two purposes – first, to shield the electrostatic noise generated by the output rectifiers (shown in purple in Figure 1), and secondly, to provide a large conduction area for the ground of the output with low impedance.

The lower part of the plane is used just to keep the noise from interfering

with the control circuit. None of the high-frequency or high-current waveforms are allowed to flow through this part of the ground plane. This preserves the integrity of the ground. The two separate

Figure 4: Using a Single Ground Plane can Degrade Ground Integrity

parts of the plane are connected by a single trace on the PCB.

#### Layer Choices for PCB Planes

If you have two or more layers on the PCB, you have choices as to where to put the shielding planes. There are several design philosophies that may be used in choosing where you put the plane layers.

I always like to have access to all the trace routings in order to be able to see all of the waveform nodes, and sometimes to make changes on the early iterations of the PCB. For complicated boards, this can tie up the top and bottom layers of the circuit board, requiring the ground and shield planes to be placed internally. With simpler circuits, most of the traces can often be placed on one side of a double-sided board, leaving the other free for planes.

Another convenient choice is to put the ground plane under the control circuitry on the top layer of the PCB. This provides a local ground connection for probing

the circuit with short lead lengths. If you are using SMT components, you will not be able to put a plane on that same layer if the component density is high. The resulting

compromise solution is to

place each plane

individually, taking

care of functionality and practical aspects at the same time. There is no single optimal solution for every design. Think carefully about the role of each part of a plane. With a two-layer board, a good solution can usually be found.

The outline of the planes should be placed on the board manually, thinking carefully about the components that need to be shielded from either generating or being susceptible to noise. Once the CAD system has filled in the area of the plane, ensure that all parts of the plane are properly connected and that isolated islands and long connections have not been inadvertently generated. Occasionally, traces will need to be rerouted to keep the planes reasonably intact.

It is important not to just pour planes across the entire expanse of the board, even if the layers and space are available. Planes that are designed to protect sensitive circuits should not be continued in the areas where there are noisy components, or they may do more harm than good.

#### Summary

The last few articles of this series have shown the nine critical rules for good PC board layout. The last step, placing power and ground planes for EMI control, is a process that involves intimate knowledge of the operation of the power circuit, and cannot be automated. It takes a lot of experience to do this effectively. Following these nine critical rules will help achieve good results on your first boards. Laying out a good circuit board for power supply design is a skill that takes years to acquire, and the timeconsuming nature of this task should never be underestimated. With each new power supply design, anticipate at least two iterations of the PC board. This is true even if there are no changes to the circuit schematic. If you are new to power supply design, it is highly recommended to begin to learn the art and science of power supply board layout as early in your career as possible. This is a very valuable skill that will greatly increase effectiveness as a power designer.

#### References

"Power Supply Development Diary Parts I-XI", Ray Ridley, Power Systems Design Magazine, 2010.

Author: Dr. Ray Ridley President **Ridley Engineering**

www.ridleyengineering.com

## **HIGH POWER SYSTEMS**

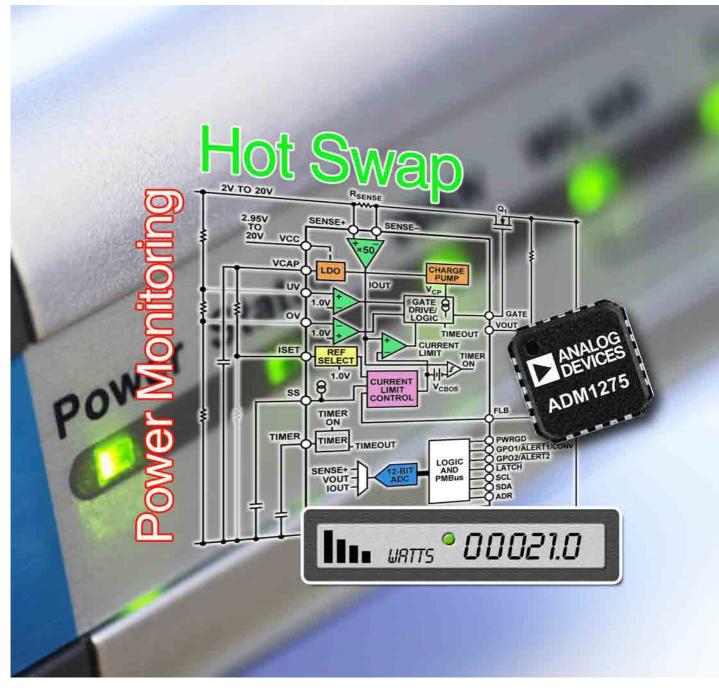

### High accuracy Hot-Swap and power monitoring

#### By Marcus O'Sullivan

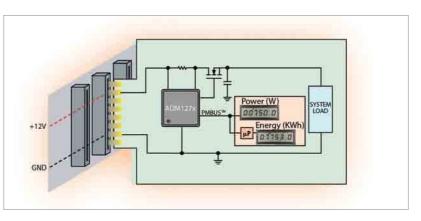

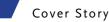

Many high power systems require the use of a hot-swap device to safely control of the inrush currents at powerup and provide fault protection.

hese circuits are commonly found in systems such as servers, network switches, redundant-arrayof-independent-disk (RAID) storage, and other forms of communications infrastructure that need to remain fully operational through their working life. These systems are known as high-availability systems. In the event of a component failure, the component will need to be removed from the system and replaced with a fully functional component, all while the power remains on and system remains operational. This process is known as hot swapping, or hot plugging.

In order to safely facilitate this event, a hot-swap controller is required to control the inrush current and prevent interruption of the backplane supply to other systems. During normal operation the controller also

#### Figure 1

provides protection against short circuits and other overcurrent faults. Analog Devices latest range of hot-swap controllers, also integrate a high accuracy digital power monitor which can facilitate high accuracy system power metering. See Figure 1.

As the power requirements for these systems are growing, efficiency is becoming more significant. Also the practicality of designing around loose tolerance and high insertion power loss is becoming more difficult. The

ADM1275 not only provides high accuracy power monitoring to report the system power, but also has many features specifically designed to reduce the losses typically associated with hotswap, such as insertion losses of sense resistors and MOSFETs.

Let's look at the design process, including component selection considerations, for a typical high current blade server hot-swap design.

**System Specifications** The following conditions are

### MOTOR CONTROL

Mitsubishi Electric offers a big variety of Power Semiconductors for a wide range of Industrial Motor Control applications from 0.4kW to several 100kW. Besides IGBT Modules also Intelligent Power Modules (IPM) and Dual Inline Package IPM (DIPIPM™) are available with extended voltage ratings.

Stand 12-421

Cover Story

#### assumed for this example:

- Controller =  $ADM_{1275}$

- VIN = 12 V Nominal

- VMAX = 12.6 V

- ITRIP = ~70 A

- CLOAD = 5000 µF .

- $TAMAX = 65^{\circ}C$

- RPOWERUP =  $10\Omega$  (static load resistance during system power up)

To simplify this example, the calculations exclude many component tolerances. These tolerances should of course be considered when designing for worst-case conditions.

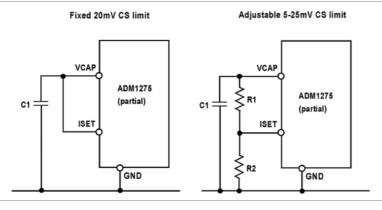

#### Sense Resistor Selection

The sense resistor chosen is primarily based on the required circuit breaker trip current. However, the ADM1275 also includes an adjustable current limit threshold which allows for fine tuning of the current limit beyond that provided by the limited availability of standard sense resistor values. The sense voltage can be programmed within a 5mV to 25mV range. Such a low sense voltage, along with the flexibility of programmability, offers reduced power loss and size in sense resistor selection.

The circuit breaker timer (current fault glitch filter) begins is typically 0.8mV below the regulation point. This means that to set a trip point of 70A(19.2mV)we need to set the regulation point to ~73A (20mV).

This is not a common available

$$R_{SENSE} = \frac{V_{SENSE}}{I_{TRIP}} = \frac{0.020 \text{ V}}{73 \text{ A}} \approx 0.273 m\Omega$$

value so the closest to consider is 0.25m $\Omega$ , with 2x 0.5m $\Omega$  in parallel. Lets reverse the equation above to determine the required sense voltage.

$V_{SENSE} = R_{SENSE} \times I_{TRIP}$  $= 0.25m\Omega \times 73 \approx 18.25mV$

The ISET pin can be programmed to a desired voltage using a divider from the VCAP reference. See Figure 2. ISET voltage = Vsense x 50.

$V_{ISET} = V_{SENSE} \times 50 = 18.3 mV \times 50 = 0.915V$

#### Therefore power can be calculated as:

$$P_{RSENSE} = I_{TRIP}^{2} \times R_{SENSE}$$

$$= (42 \text{ A})^{2} \times 0.0005 \Omega$$

$$= \sim 0.882 \text{ W}$$

So each sense resistor should be capable of dissipating >1 W (including temperature derating factors). A 2W or 3W resistor is recommended to reduce running temperatures.

A series of  $10\Omega$  resistors should be used to average all these nodes together to the controller.

#### Figure 2

Using the VCAP reference of 2.7V and assuming  $R_1 = 100 k\Omega$ , this will result in a bottom resistor of 51.1k $\Omega$ . The given ISET voltage provides a circuit breaker trip point of ~70A and a regulation current set point of 73A.

Assuming worst case DC current could be as high as 75A (including tolerances), the maximum DC current for each resistor can be given as ~42A, including ~10% to account for imbalance.

Summary of the key component selection for this section RISET(TOP) =  $100 \text{ k}\Omega$ RISET(BOT) =  $51.1 \text{ k}\Omega$ RSENSEx =  $0.5m\Omega x_2 (2 / 3W)$  $RAVGx = 10\Omega x_4$

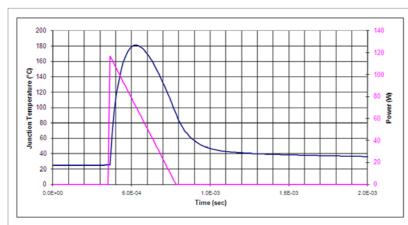

#### MOSFET Selection

The first consideration as criteria for selection of a suitable MOSFET is the RDSON specification, to ensure that minimum power is lost in the MOSFET when it is fully enhanced in normal operation. The ADM1275 features a high

14 WWW.POWERSYSTEMSDESIGN.COM

The power modules feature state of the art CSTBT<sup>™</sup> chip technology and new free wheel diode chips in a flexible package design as well as a high power cycling capability to ensure highest reliability and efficiency. With easy to use features, compact size and a high robustness they completely fulfill the markets needs.

for a greener tomorrow

voltage gate drive to ensure a minimum of 10V VGS is achieved to maintain the lowest specified RDSON. The gate drive circuit is designed to achieve this while still ensuring the 20V maximum VGS spec is not violated during fault conditions.

As the temperature of the MOSFET increases, its power rating is reduced, or derated. The RDSON spec determines the maximum junction temperature of the MOSFET and therefore the required derating can be applied to SOA parameters. In addition, running MOSFETs at high temperatures may decrease their reliability.

Let's begin by estimating the required RDSON. Recall the maximum DC current was 75A, worst case. Then using the maximum ambient temperature specified in section 1 we can estimate the power loss in the MOSFET(s).

First we make a few assumptions:

- RthJA = 40 C/W (maximum)

- TjMAX = 120 °C

(This is the maximum preferred junction temp, keeping well away from any silicon limits)

Calculate the junction temperature rise:

Then the power for a single FET:

$T_{RISE} = T_{iMAX} - T_{AMAX} = 120 - 60 = 60^{\circ}$ C

Now total RDSON:

$$P_{MOSFET} = \frac{T_{RISE}}{R_{thJA}} = \frac{60}{40} = 1.5W$$

This number is far too small for 15

$$R_{DSON} = \frac{P_{MOSFET}}{I_{MAXDC}^{2}} = \frac{1.5}{75^{2}} = 0.266m\Omega$$

a single FET so let's try 3 FETs in parallel:

Now we subtract 10% to give us

$$R_{DSON} = \frac{P_{MOSFET}}{(I_{MAXDC}/3)^2} = \frac{1.5}{25^2} = 2.4m\Omega$$

some margin for imbalance due to layout asymmetry and a further 1.4 factor to allow some derate:

$$R_{DSON} = \frac{2.4 \times 0.9}{1.4} = 1.5m\Omega$$

this as our target RSDON we can now search for suitable candidates The search can be narrowed to FETs that fit the following profile:

Taking

- VDS = 25/30V (20V may be possible but not preferred)

- VGS = 20V

- RDSON  $\leq 1.4 \text{m}\Omega$

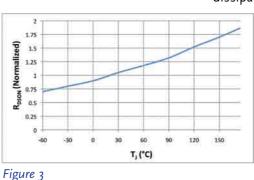

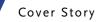

After selecting a suitable MOSFET, the derating of the RDSON should be quantified using the MOSFET datasheet graph of RDSON against TJ.

Using TjMAX of 120 °C, we can see from Figure 3. the RDSON increases by a factor of ~1.52, to about 1.824m $\Omega$ (assuming 1.2m $\Omega$ at 25°C) at 120°C. As a rule its preferred to keep junction temp ≤120C to increase reliability.

Assuming that the MOSFET's max RDSON is 1.83m $\Omega$ , the power of each FET can be:

$$P_{MOSFET} = \left(\frac{I_{MAXDC}}{n} + 10\%\right)^2 \times R_{DSON}$$

$$= (27.5 \text{ A})^2 \times 0.00183 \Omega$$

$$\approx 1.39 \text{ W}$$

This is determined by the MOSFET's thermal resistance at ambient temperature should be specified in the datasheet. The footprint size, airflow, nearby heat sources and additional copper will also have an effect on this value so care must be taken to ensure the specified conditions are met. Assume, for this design a target of:

$R_{th I4} = 40^{\circ} \text{C/W}$

(Note: Care should be taken to ensure layout/airflow does not exceed this figure)

As the MOSFET is expected to dissipate ~1.39W, a worst-case temperature rise of 55.6°C above ambient can be expected as

follows:

$T_{RISE} = R_{thIA} \times P_{MOSFET} = 55.6^{\circ} \text{C}$

The resulting junction temp of the FET can be determined as follows:

## **Powerful Products** For Powerful Electronics.

Power Distribution **S**vstems

The newest addition to the RO-LINX® family

0

## Learn More About our **Power Electronics Solutions by** Booth #12-439.

Europ

Visiting us at

#### PDS

TMS

Power Distribution Systems specializes in the design and manufacture of custom designed busbars. Rogers' newest addition to the RO-LINX® family, the RO-LINX® PowerCircuit™ busbar, addresses the needs of emerging applications in the (H)EV, commercial solar and low voltage variable frequency drives market.

The RO-LINX PowerCircuit busbars key benefits for these applications are:

- 3D Capabilities / Compactness

- Higher Current Density (100-500 amp)

- Medium to High Volume Component • Assembly Processes

#### Empowering your energy.

For more information visit us at: Thermal Management Solutions (TMS) | www.rogerscorp.com/tms Power Distribution Systems (PDS) | www.rogerscorp.com/pds

Thermal Management **S**olutions

Rogers HEATWAVE<sup>™</sup> high performance AlSiC materials combine excellent thermal conductivity and controlled thermal expansion with low density and high stiffness to match the performance characteristics of modern power semiconductor device packaging solutions and systems.

- Improves Longterm Reliability

- **Reliable Thermal Performance**

- Ease of Integration into Applications

- High Stiffness & High Mechanical Stress

USA +1-480-917-6137 EUROPE +32-9-235-3611 ASIA + 65-6747-3521

$T_J = T_A + T_{RISE} = 60 + 55.6 = 115.6^{\circ}$ C

As this is below the maximum selected value of 120°C, the risk of thermal runway should be avoided. When using multiple MOSFETs in parallel, a  $10\Omega$  resistor should be use in series with the gate of each MOSFET to prevent parasitic oscillations.

Summary of the key spec / component selection for this section:

| QX    | = Selected 1.2m $\Omega$ MOSFET. |  |

|-------|----------------------------------|--|

| RthJA | = 40 k/W                         |  |

| RGATE | $= 10\Omega (x_3)$               |  |

#### **Power Derating Factor**

Now that the maximum junction temperature is verified we can determine the maximum derate factor. This number will be used to derate all the SOA parameters to verify a robust solution across temperature.

To determine the maximum expected case temperature we can use:

$$T_{C} = T_{j} - (R_{thJC} \times P_{MOSFET})$$

$$T_{C} = 115.6 - (1.0 \times 1.4) = 114.2^{\circ}C$$

Now the derating factor can be calculated as follows:

$$DF = \frac{T_{J_{\text{max}}} - T_{CSOA}}{T_{J_{\text{max}}} - T_{C_{\text{max}}}} = \frac{175^{\circ}\text{C} - 25^{\circ}\text{C}}{175^{\circ}\text{C} - 114.2^{\circ}\text{C}} = 2.46$$

Summary of the key spec / component selection for this section: DF = 2.5

#### Foldback

The ADM1275 utilizes a foldback

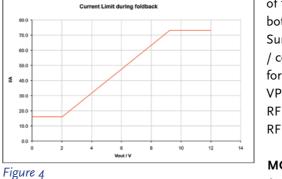

technique to protect the MOSFETs in the event of overcurrent faults or short circuits. The output voltage is monitored using a divider on the FLB pin and the current limit is adjusted based on the VDS of the MOSFET. An example of this relationship can be seen in Figure 4.

When the output voltage is at zero, there is a lower limit clamp to prevent the current limit approaching zero. This clamp is fixed at 0.2V on the FLB pin (or 4mV Vsense), which equated to ~16A on this particular design. As the output voltage increases, the current limit ramps as a function

of the output voltage. This threshold is set by the divider on the FLB pin, using a reference equal to VSENSEREG X 50. This voltage should be chosen to be low enough to avoid any expected VOUT load steps from affecting

the current limit. The Figure 5 PWRGD output is also derived from the voltage level at the FLB pin.

Targeting 10.3V, we get a divider

of  $100K\Omega$  top and  $12K\Omega$ bottom.

Summary of the key spec / component selection for this section:

VPG = 10.3V RFLB\_TOP  $= 100 k\Omega$ RFLB\_BOT = 12kΩ

#### **MOSFET Safe Operating** Area analysis

The next step is to review the SOA curve on the MOSFET datasheet to determine how much time it can tolerate the worst case power in the FET. This will determine a suitable timer capacitor value.

In a multiple FET solution, it must be assumed that a single FET could be dissipating 100% of the power during a powerup or vent such as these. This is due to possible differing Vth levels on each FETs, only one could be conducting when in regulation. If a short was applied the Vds of the FET can be assumed to be ~12.6V (assuming source

at GND). In reality the number would likely to be lower than this due to line impedance.

However, if we look at the profile

## **Extend Your Battery Life!** with Micrel's "Green Power" Regulators

**MIC23155** delivers extremely high efficiency for portable products and green home/office appliances. Micrel's HyperLight Load® Regulators save precious power over the entire load range for 'Green' Devices.

The MIC23155 features internal MOSFETs able to deliver up to 2A output current while consuming just 23µA of guiescent current inside an ultra small 2.5mm x 2.5mm Thin MLF® package.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel. com/ad/mic23155.

#### Ideal for use in:

- ◆ Mobile handsets

- Portable media/MP3 players

- Portable navigation devices (GPS)

- WiFi/WiMax/WiBro modules

- Solid State Drives/Memory

- Wireless LAN cards

- Portable applications

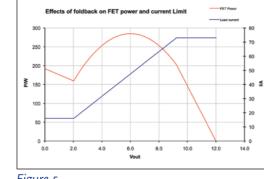

of the FET power against Vout we see that the relationship is not monotonic. See Figure 5. The worst case power in the FET is shown at approximately 6.3V (50% of Vin). The current can be easily calculated using the following equation:

$$\begin{split} V_{FLB} &= V_{OUT\_WCP} \left( \frac{R_{FLB\_BOT}}{R_{FLB\_TOP} + R_{FLB\_BOT}} \right) \\ &= 6.3 \times \left( \frac{12,000}{100,000 + 12,000} \right) = 0.675 \\ I_{FLB\_WCP} &= \frac{V_{FLB}}{R_{SENSE} \times CS_{GAIN}} = \frac{0.675}{0.25m\Omega \times 50} = 54. \end{split}$$

(WCP=Worst Case Power)

Now derate this by Derate Factor of 2.5 and we get 135A. So if we go to the SOA diagram of the

#### Figure 6

MOSFET, and intersect 6.3V with 135A, we get approximately 0.8ms. See Figure 6.

It should be noted that some FETs SOA power lines do not always represent a constant power

product. This should be checked and if the line is not constant power then more points should be checked. For example, check VMAX of 13.2V against IFLBMIN = 16 A, derated to 40A. In this case the 6.3V SOA is very similar. If there is no specific requirement for the fault filter, its recommended to further reduce this to account for SOA tolerances and inaccuracies. In this case, lets reduce by 50% to o.4ms.

Summary of the key spec / component selection for this section:

TSOA\_MAX = 400µs

Powerup analysis

Now that the timer had been selected, we must check to verify that there is sufficient time available to allow the loads caps to complete powerup. This is determined by how long the startup current profile intersects with the current limit ... i.e. how long the timer is active during powerup.

During the power-up phase, the controller will usually hit the current limit due to the inrush current demanded by the

load capacitance. If the time set by the TIMER pin is insufficient to allow the load capacitors to charge, then the MOSFET will be disabled and system will not power up. We can use the following equation to

estimate the powerup time using an average current limit across the foldback system:

$$t_{CHARGE} = \frac{C_{LOAD} \times V_{MAX}}{I_{AVERAGE} - \frac{V_{MAX}}{R_{POWERUP}}}$$

$$= \frac{5000 \times 10^{-6} \text{ F} \times 12.6 \text{ V}}{33 \text{ A} - \frac{12.6}{10}}$$

$$\approx 1.98 ms$$

As the time required exceeds the determined SOA limits, the system would not complete powerup into this size load capacitance. To overcome this the inrush current needs to be lowered to a level below the hotswap control limit at powerup. This is achieved by increasing the effective gate capacitance resulting in a slower powerup time and a lower inrush current. In this way the inrush is controlled using an open loop source follower system. To avoid exceeding the current limit(16A), an additional gate capacitor can be determined as follows to provide an inrush of ~10A:

$$C_{GATE} = C_{LOAD} \times \left(\frac{I_{GATE}}{I_{INRUSH}}\right)^{\frac{1}{2}}$$

$$= 5mF \times \left(\frac{25\mu A}{10A}\right)^{\frac{1}{2}}$$

$$\approx 12.5nE$$

The effective CGD of the MOSFETs can be subtracted from this figure. However, to account for tolerances we can round up to 15nF.

#### Powerup time can now be calculated as follows:

$$t_{POWERUP} = \frac{C_{GATE} \times V_{MAX}}{I_{GATE}}$$

$$= \frac{15\text{nF} \times 12.6 \text{ V}}{25\mu A}$$

$$\approx 7.5 \text{ms}$$

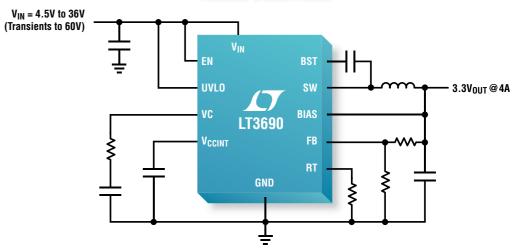

## 36V, 4A Sync Buck

#### **Actual Schematic**

### $70\mu A I_{O}$ , <15mV<sub>P-P</sub> Output Ripple and 92% Efficient

The LT<sup>\*</sup>3690 brings a new level of performance and features for high voltage point-of-load step-down conversion. Its wide input voltage range of 3.9V to 36V, with 60V transients, meets the needs of many of the rails common to industrial, medical and automotive applications. Up to 4A of continuous output current can be supplied to the load with minimal thermal design. Its 70µA of quiescent current in standby maximizes battery life in "always-on" applications. With up to 1.5MHz switching frequency and a high level of integration, the external components are few and small, enabling a compact solution footprint.

(Actual Size)

#### **Features**

- Input Voltage Range:

- 3.9V to 36V (60V Transients)

- 4A of Continuous Output Current

- Quiescent Current of 70µA  $(12V_{IN} \text{ to } 3.3V_{OUT})$

- Low Output Ripple of  $< 15 \text{mV}_{P-P}$  in Burst Mode<sup>®</sup> Operation

- Programmable Switching Frequency: 170kHz to 1.5MHz

- Output Voltage Range: 0.8V to 20V

- Programmable Input Undervoltage Lockout

- Compact 4mm x 6mm QFN Package

Europe Sales offices: France 33-1-41079555 Italy 39-02-38093656 Germany 49-89-9624550 Sweden 46-8-623-1600 UK 44-1628-477066 Finland 358-9-88733699 Distributors: Belguim ACAL 32-0-2-7205983 Finland Tech Data 358-9-B873382 France Arrow Electronique 33-1-49-784978, Tekelec Airtronic 33-1-56302425 Germany Insight 49-89-611080,

(20mm x 15mm)

V Info & Free Samples LT3690 Demo Circuit www.linear.com/3690 +49-89-962455-0 IT LINEN

[7], LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Setron 49-531-80980 Ireland MEMEC 353-61-411842 Israel Avnet Components 972-9-778-0351 Italy Silverstar 39-02-66125-1 Components 57/2-57/36-037 Hand Statesting Streets 57/2-0612-71 Netherlands ACAL 31-0-402502602 Spain Arrow 34-91-304-3040 Turkey Arrow Elektronik 90-216-4645090 UK Arrow Electronics 44-1234-791719, Insight Memec 44-1296-330061

Summary of the key spec / component selection for this section: CGATE = 15nF TPOWERUP =~ 7.5ms

#### **Timer Capacitor**

Now that the MOSFETs SOA requirements have been determined, and powerup time is satisfied, a TIMER capacitor value can be calculated. This can be calculated as follows:

$$C_{TIMER} = \frac{t_{TIMER} \times I_{TIMER}}{V_{TIMER}}$$

Where ITIMER =  $60 \mu A$  and VTIMER = 1.0 V,

$$C_{TIMER} = \frac{(400 \times 10^{-6} \text{ s}) \times (60 \times 10^{-6} \text{ A})}{1.0 \text{ V}}$$

Power in MOSFET at startup Now, as a final step we need to check that the power being dissipated in the FETs at startup is within the SOA limits of the MOSFET. We can calculate the Energy required to charge the load capacitor as follows:

$$E_{CL} = \frac{CV^2}{2}$$

=  $\frac{5000 \times 10^{-6} \times (12.6)^2}{2}$

\$\approx 0.397 joules

The power can be determined using:

$P_{FET} = \frac{E}{t}$ 0.397  $=\frac{0.597}{7.5\times10^{-3}}$  $\approx 53W$

(where t = 7.5 ms)

Derate this to 133W. Now calculate the current at average Vds (VINMAX / 2):

$$I = \frac{P}{V} = \frac{133}{6.3} = 21.11A$$

**Design Complete!**

Now if we examine the SOA again, we can see that 6.3V and 22A corresponds to >10ms, satisfying SOA limitations.

Here in Figure 7 is the complete design for the main circuit components.

Author: Marcus O'Sullivan Applications engineer, Power Management Group Analog Devices

www.analog.com

Figure 7

Brand\_new\_Design

DIGITAL POWER

## DIGITAL POL IMPROVES KEY METRICS

### Current-sharing second-generation advantages

#### By Patrick Le Fèvre

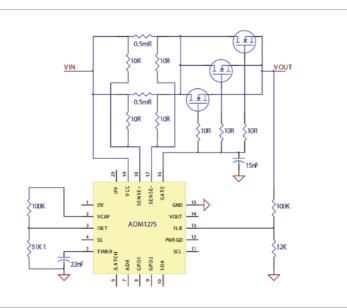

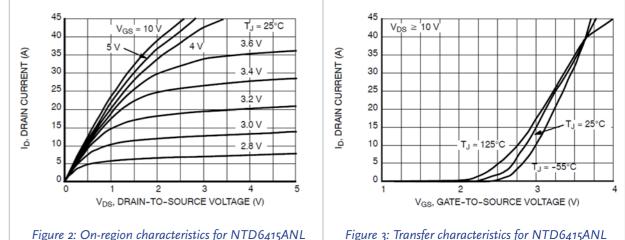

Digital power conversion has moved on from being a novelty to widespread acceptance. Ericsson launched its BMR453 quarter-brick intermediate-bus converter in 2008 and followed with an eighth-brick version together with a pair of point-of-load regulators (POLs). Each of these 3E family devices introduced electrical specifications and features remain best-in-class.

he key metrics in power engineers' thinking -whether in consumer appliances or datacenters- are conversion efficiency, power density, and electrical performance. Balancing these elements alongside other considerations—such as feature sets and cost—requires multiple compromises. For instance, because passive components dictate any conventional analogue converter's loop dynamics, designers set the operational "sweet spot" at 50 - 70% of the converter's output potential, as this is where users have previously applied such products.

By implementing a digital control architecture that adapts to line and load conditions in real time, the first-generation BMR450 extends conversion efficiency particularly under light loads, where losses predominate. The digital converter employs adaptive dead-time control for its synchronous buck converter's switches, which safely minimises the period between the MOSFETs being off-during which time currents flow through the devices' lossy body diodes. The strategy enhances efficiency at operational extremes and helps to flatten the efficiency curve. The BMR463 adds programmable

strategies to optimise efficiency under light loads by minimising the effective switching frequency and preventing energy-sapping negative current flow through the lower MOSFET switch. Other new features reflect improvements to the underlying silicon together with proprietary firmware developments. Importantly, the new converter is specified for 4.5 - 14 VDC input and 0.6 - 3.3 VDC output levels to satisfy the wider range of conditions that today's applications demand. Figure 1 shows performance for the conventional 12 VDC intermediate-bus rail and a nominal 5 VDC input level,

Figure 1: The BMR463 extends the operational envelope to accommodate 4.5 – 14VDC input and 0.6 – 3.3VDC output levels.

reflecting the trend towards lower bus voltages due to their potential for optimising system conversion efficiency.

#### Digital core delivers dramatic power-density and functionality improvements

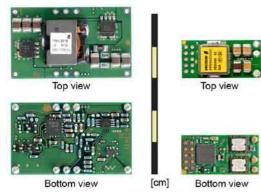

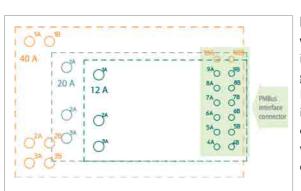

Better efficiency and digital control's greater integration permit a step-function improvement in power density, as figure 2 illustrates for the BMR450 and its

Figure 2: The first-generation digital BMR450 (right) squeezes 20A from a compact outline that improves power density from the analogue converter's 7.4W/ cm3 to 24.3W/cm3

analogue PMH8918L predecessor:

Apart from tripling power density, the BMR450 integrates a supervisory measurement and control subsystem that the device's PM-Bus interface makes accessible massively shrinking circuit-board complexity and area compared with any conventional analogue architecture. Board power management logic can interrogate

> any 3E family device to read parameters such as output voltage, current, and converter temperature, and can program the device in a running system.

> > The BMR463 adds a "snapshot" mode that reads key operating parameters and stores them to nonvolatile memory during normal

operation, and that can be set to operate automatically under fault conditions. Designing sophisticated PMBus systems is now easier than ever and the potential benefits are huge—ranging from dynamic system optimisation that can drive down energy consumption to data acquisition that enables root-cause and predictive failure analysis.

### Transient response complements basic electrical performance

The BMR463's electrical performance is typically better than analogue converters of similar power levels. Line and load regulation remain within 3mV at any setting, while output voltage accuracy including temperature effects over the -30 to +85°C operating range is within  $\pm 1\%$ . Output ripple and noise vary from 20mV peak-to-peak at 0.6V outputs to 60mV at 3.3V and can be optimised for specific applications by adjusting the converter's default 320kHz switching frequency from 200 – 640kHz.

In the event of a fast output current step, the digital core's nonlinear response loop bypasses the main control loop, increasing the converter's gain-bandwidth product to speed transient response beyond the capabilities of a linear loop. Unlike any conventional analogue POL, it is possible to fine-tune the digital loop's default dynamic characteristics to optimise transient response performance for specific line, load, and output capacitance conditions.

### Standalone and PMBus application versatility

Like all 3E family devices, the nonvolatile memory that stores the BMR463's setup parameters can be programmed during initial manufacture or later-such as once during a host board's ATE functional tests, or arbitrarily during system operation-to set its output voltage and other parameters via its PMBus interface. The device's "set-&-forget" capability is useful for implementing the power-rail sequencing that multi-rail logic devices require, as well as any slew rate limiting that may be necessary to minimise power transients at system power-up. Also capable of operating in standalone mode for replacing analogue converters, the BMR463's communications header includes pins that support remote voltage sensing, together with a pinstrap that allows one resistor to set the device's output voltage between 0.6 - 3.3 VDC in 28 increments.

At 25.65 x 13.8 x 8.2mm—0.9mm wider than the BMR450-the BMR463 adds two pins that extend its versatility. A group communications bus (GCB) pin allows multiple BMR463s to communicate autonomously. One application is to allow appropriately-configured devices to implement fault spreading, such that a temporary fault in any one converter initiates a predetermined shutdown and restart sequence that protects sensitive multi-rail chips; another is to sequence the application of voltage rails in multi-rail environments during routine power up/down events. Also simplifying multi-rail applications, an analogue voltagetracking input complements the normal voltage sequencing so the device can track an external reference voltage and ramp its output at the same rate, or at a percentage of that rate.

The BMR463's clock synchronisation adds the ability to shift phase angle between devices switching in up to 16 increments, reducing instantaneous loading on the input supply as current peaks are spread out across a whole switching period. The converter now includes a dedicated power-good signal that signifies when the output is within -10/+15% of its target value; these default limits are configurable.

Autonomous current sharing without OR-ing diodes The BMR463 introduces a current-sharing mode that allows up to eight device outputs to be connected in parallel without any OR-ing diodes or MOSFETs to deliver up to 160A. This benefits systems that dynamically power down circuit blocks to minimise static power consumption, such as in response to network traffic patterns in communications systems.

When configured as a currentsharing group, the BMR463 with the lowest position within the group automatically acts as a reference that continuously broadcasts its inductor current via the GCB. Other group members assess this information and adjust their output voltages to maintain equal current delivery between each device. Some artificial droop resistance in each device's output voltage path enables automatic compensation for inequalities such as differing circuit-board resistance paths.

Group members can autonomously set up switching phase differences between them that minimises input-rail stresses and divides the output ripple level by the number of devices in the group. In addition, a currentsharing group is able to dynamically add or shed phases in response to load conditions. This can save conversion switching energy under light loads when fewer BMR463s are necessary to service the output current demand. A group can also provide redundancy, dropping faulty

Future precision. Future performance. Now available.

### CAS-CASR-CKSR

The transducers of tomorrow. LEM creates them today. Unbeatable in size, they are also adaptable and adjustable. Not to mention extremely precise. After all, they have been created to achieve great performance not only today - but as far into the future as you can imagine.

- Several current ranges from 6 to 50 A<sub>BMS</sub>

- PCB mounted

- Up to 30% smaller size (height)

- Up to 8.2 mm Clearance /

- Creepage distances +CTI 600 for high insulation

- Multi-Range configuration

- +5 V Single Supply

- Low offset and gain drift

- High Accuracy @ +85°C

- Access to Voltage Reference

- Analog Voltage output

#### www.lem.com

At the heart of power electronics

| Function                       |

|--------------------------------|

| Input voltage                  |

| Power ground                   |

| Output voltage                 |

| Voltage tracking input         |

| Pin-strap ground reference     |

| Positive sense                 |

| Negative sense                 |

| PMBus address pin-strap        |

| Group communication bus        |

| PMBus clock                    |

| PMBue data                     |

| Output voltage pin-strap       |

| Synchronization VO             |

| PMBus alert                    |

| PMBus control (Remote Control) |

| Power Good                     |

| PMBus address pin-strap        |

|                                |

#### Figure 3: A common footprint can accommodate 12, 20, and 40A BMR46x family devices.

phases and switching in replacements-when the group will selfconfigure to maintain normal operation if it can supply the necessary load current.

#### Footprint and packaging practicalities

Ericsson's designers have evolved a footprint for the BMR463 that makes provision for upcoming BMR46x devices that will extend the output current levels to include 12, 20, and 40A. Figure 3 shows this approach. Board designers can use a uniform footprint to accommodate power level changes when implementing system upgrades. Each BM-R46x is available in through-hole or surface-mount versions, and designed to ease automated assembly using standard board manufacturing processes.

An evaluation kit is available that provides a PCbased development environment to explore PMBus applications built around 3E family devices.

#### Author: Patrick Le Fèvre Marketing & Communication Director Ericsson Power Modules

For further application information on digital power conversion, please navigate to

www.ericsson.com/powermodules

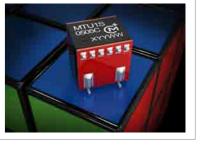

## SMD CUBE SKRINKS FOOTPRINT

### Much-improved 1W isolated DC/DC converter

### By Ann-Marie Bayliss

With their ability to drastically simplify provision of lowpower isolated power rails that are commonly required in applications such as process control and industrial communications interfaces, encapsulated though-hole DC/DC converters became immensely popular following their introduction more than two decades ago.

esigning a tiny DC/ DC converter that meets contemporary performance expectations and that provides a degree of future-proofing is not straightforward. The first challenge is to select a topology that meets the size constraints that miniaturisation demands, yet is capable of adequate output power delivery, isolation and regulation. The chosen approach should be able to address a range of common input and output voltages as well as ideally being extensible to deliver more power from a similar platform. The need for an isolation barrier that withstands typically 1 kVDC implies transformer

coupling that requires ac primary drive and secondary rectification whose implementation inevitably involves compromises that mainly lie between component count and conversion efficiency.

The conventional minimum component count approach uses a saturating 'Royer' circuit, a self-oscillating pushpull topology, in which a pair of bipolar transistors drive antiphase primary transformer windings and derive their base currents from opposite ends of a centretapped auxiliary winding. Applying a dc input voltage through a start-up bias circuit turns on one transistor, which remains on until

the transformer's core saturates, the transistor gain-limits and all transformer winding voltages collapse. Residual energy in the transformer causes reversal of the polarity of winding voltages which switches off the first transistor and biases the second to the 'on' condition which then starts to drive its winding to saturation. The process repeats to sustain oscillation at a frequency that is proportional to the input voltage, creating a square-wave output voltage for rectification.

This basic circuit has several limitations, notably its lack of active regulation—the output voltage is a function of the input

#### Figure 1: The MTU1 series significantly improves output load regulation performance.

voltage, internal losses and the transformer's turns ratio together with poor efficiency due to semiconductor switching and core magnetic losses at the high frequencies that miniature transformers require. Well-known variations around the theme include modifying the circuit to avoid lossy core saturation by using a second drive transformer which has potentially higher efficiency but at the cost of complexity and size.

### Electrical specification enhancements

By combining proprietary circuit enhancements and recent component fabrication techniques, designers can improve the load regulation of such a converter. For example, Murata Power Solutions' engineers were able to increase their MTU1 part's load regulation performance to a maximum -4, +5.5% from 10% of full load upwards. By comparison, previous ranges achieved -7.5, +10% see figure 1. For many applications, the load regulation these enhancements offer obviates the need for inefficient and spacehungry linear post-regulation stages.

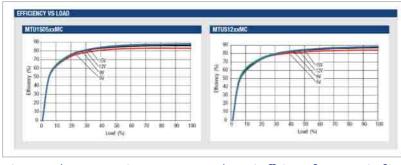

At the same time, a major improvement to the part's toroidal magnetics helps to improve efficiency to the range of 83 - 88% Also, the switching frequency has reduced from nominally 110 kHz to 82 kHz for 5V-input MTU1 parts and 90 kHz for its 12V-input variants. These steps likewise contribute towards lower dynamic losses. Notably—and as figure 2 shows-the efficiency curves reach or exceed 80% at around 40% of output power capability and are virtually flat from 50% upwards. These efficiency improvements translate into an approximately

56% reduction in internal power dissipation that reduces internal hot-spots maximising reliability while minimising the heat load that the host equipment has to accommodate. The MTU1 series requires no derating over its -40 to +85°C operating range. Other electrical specification enhancements include reduction to reflected

ripple current from around 30 mA peak-to-peak to 5 – 6 mA and isolation capacitance reduction of between two and three times. These attributes greatly ease input filtering needs. The reduced capacitance further isolates input and output, making the part far less susceptible to transmitting noise through its isolation barrier which could potentially disturb sensitive loads.

### Design for manufacture achieves MSL1

Significantly—and unlike some plastic-encapsulated packages that industry-standard components employ—the MTU1's composite assembly has a level 1 rating for moisture sensitivity (MSL1).

Figure 2: The MTU1 series meets or exceeds 80% efficiency from  $\sim 40\%$  of its output power capability upwards.

Figure 3: The MTU1's cube-like package achieves MSL1 and eases automated assembly.

Moisture absorption and retention is a major issue for many surface-mount devices as it can generate large stresses when the part is subjected to a rapid and very large temperature rise, such as during lead-free reflow processing that can reach peak temperatures as high as 245°C. The resulting outgassing can easily destroy the device and is generically known as "popcorn cracking".

As a result, component manufacturers classify the moisture sensitivity of their parts on a scale that IPC/ JEDEC J-STD-20 rates from 1 through 6, where an MSL1 rating signifies that the part is immune to popcorn cracking regardless of its exposure to moisture. The MTU1's package design dispenses with the prebaking procedures that many parts rated less than MSL1 routinely require and that can negatively impact upon their solderability. Additionally, for MSL1 rating, no expensive handling and storage precautions are necessary. Furthermore, the MTU1's open-frame construction is designed to reflow safely during processing and negate any tendency towards internal solder bridging, while the cube shape's flat top surface makes it easy for standard vacuum pick-&-place nozzles to manipulate.

Author: Ann-Marie Bayliss Product Marketing Manager Murata Power Solutions www.murata-ps.com

## World's Largest Exhibition

for

Electrical Insulation Materials

Electromagnetic Coil, Electric Motor

### Electric Transformer Manufacture & Repair

### **CWIEME Berlin 2011** 24 - 26 May 2011

Messe Berlin - Germany

Register NOW - FREE www.coilwindingexpo.com

email: tickets@coilwindingexpo.com Tel: +44 (0)1481 822909 Fax: +44 (0)1481 823292

## **DIRECT FUEL INJECTION**

### Implications for automotive MOSFET devices

#### By Don Zaremba

There is a pressing need within the automotive industry for realizing greater degrees of fuel economy. This is being driven by rising oil prices through ongoing political uncertainty in many oil producing countries.

here are growing difficulties in extracting remaining oil reserves and increased sales within emerging markets such as China, Russia, Brazil and India married with intensifying environment concerns. In an attempt to stem pollution levels, the US Environmental Protection Agency (EPA) has set guidelines that from 2012 onwards fleet-wide greenhouse gas emissions should be cut by 5% each year. At the same time car manufacturers still need to meet customer expectations in terms of performance, so that they can keep ahead of their competitors. This is certain to put a great deal of pressure onto manufacturers' engineering teams, and will call for more innovative solutions that can tackle these disparate demands. Maximizing the effectiveness of every drop of fuel is something that no car maker can now afford to ignore.

One way that fuel efficiency can be improved is to make enhancements to the fuel delivery mechanisms being utilized. The following article will look at how the latest car models will be able to achieve this goal and describe the supporting electronics involved.

#### Modern fuel delivery systems

Modern engine designs are now starting to employ direct-injection Here fuel is introduced straight into the cylinder rather than being premixed outside. This technique has major advantages as it allows more accurate control of the quantity of fuel used and the injection timing, leading to an increase in the vehicle's horsepower combined with a lower fuel intake. As a result of implementing direct-injection, car manufacturers will be able to meet government guidelines for reducing vehicle emission levels while still producing the high performance cars customers want. However direct-injection calls for even more sophisticated control electronics and puts exacting demands on the components being utilized.

Traditionally electronic fuel injection would be carried out via a solenoid-based injector. This method has proved to be both inexpensive and highly reliable. As a result it still sees widespread use today. Unfortunately it is also relatively inefficient. There is a growing trend toward the implementation of piezoelectric injectors - with fine, rapid, multiple injections allowing the greater fuel delivery control desired, but they can prove expensive and require high voltages to activate. The car market has become increasingly competitive in recent years, with manufacturers seeing their margins tightened. Reconciling the increased cost of more advanced electronics for fuel delivery is difficult. Today's car owners

will not pay more for improved performance, they expect that already. Automotive electronics has become similar to computing and portable electronics sectors in that regard - with ever increasing functionality and performance being met by lower and lower price tags.

#### The role of power MOSFETs in modern fuel delivery systems

Power MOSFETs are normally used in fuel delivery to switch the injector on/off per commands from the ECU (Engine Control Unit). One MOSFET will be employed for each injector. As fuel delivery systems have evolved, so have the MOSFET's requirements. This has meant that semiconductor companies have been forced to develop new generations of devices that have enhanced performance in a number of key metrics.

1. Operating voltage – some MOSFET parameters for direct-injection will be notably higher than for standard injection systems. Directinjection systems generally require higher pull-in current (in order to get the solenoid operating against high cylinder pressure). This high current must happen quickly (due to limited time available to inject fuel in the engine cycle, which decreases as the RPM rises), therefore a higher voltage rail is required. Directinjection systems can have rail voltages >100 V (as opposed to around 50 V for standard injection systems). Thus higher voltage MOSFETs need to be specified, along with voltage boost power supply circuits. Piezoelectric injectors also require high voltages to be activated, typically 200 V or above. In general, there is a lack of auto-qualified MOSFETs for high/medium voltages. As piezo applications increase, module suppliers will demand a larger selection of suppliers from which to buy the required MOSFETs.

- 2. Operating current Higher currents call for lower On resistance (Rdson) devices to meet module voltage drop requirements and to reduce power dissipation in the module. Newer systems are considering trench technology (as opposed to established planar process technology) in order to reduce overall system cost. Current trench technologies can reduce active die area of a planar device with equivalent Rdson by 50%.

- Switching speeds and repetitive UIS - The timing for an engine, even running at 10,000 RPM is not that fast in electronics terms, considering that other applications, like CPU VRM switches, run at hundreds of KHz, for example. Nevertheless increasingly complex fuel delivery algorithms are causing device

3.

#### POWER SYSTEMS DESIGN APRIL 2011

switching speeds to become a more important factor. This is because the modern systems we have discussed are now injecting fuel in multiple separate bursts, instead of a single burst. The difficulty in multi-injection systems is having enough time to ramp the current again and again. If timing is not critical, the circuit designer can clamp the inductor voltage with a diode to the supply rail, thus not putting the MOSFET switch into avalanche mode at each turn-off cycle. However with increasing injections, designers often have no choice but to allow the MOSFET switch to flyback, affording maximum voltage across the solenoid inductor. This requires MOSFETs with strong **UIS (Unclamped Inductive** Switching) capabilities. Considering a MOSFET could see >1 billion injection cycles in a vehicle's lifetime, the repetitive UIS capability of the specified MOSFET is of great importance to system designers. As yet, however, the repetitive UIS capability of MOSFETs is not a well characterized parameter across the various vendors on the market. Efforts are now in progress to better understand reliability concerns, especially comparing new trench technologies to existing planar technologies. Trench MOSFET technology is often perceived as weak with

regard to UIS capability, when compared to planar MOSFET technology. One reason for this perception is a trench device with equivalent Rdson to a planar device has significantly less active die area. For a properly designed and manufactured MOSFET, UIS capability is a function of thermal capability, so a trench device will always exhibit lower UIS capability than a planar device which is equivalently Rdson rated. The geometry of the trench structure results in a more serious concern however. In high current avalanche operation, trench technology affords hot carrier injection into the gate oxide, which can result in shifted DC parameters over multiple avalanche events. These parameter shifts can be minor, but DC parameter behavior does need to be better understood over hundred of million to billions of avalanche events.

Thermal considerations -Powertrain electronics are typically housed within the ECU. The ECU's ambient temperature requirements are usually the most uncompromising in the vehicle, spanning from -40 C to 125 C or above. This means that MOSFETs with higher operating temperature specifications must be designed in, capable of dealing with broader temperature

ranges. To compound problems further, advances in fuel delivery systems (with new circuit topologies requiring high side switching, boost supply, and sometimes to switch down to the battery rail for hold current) have led to larger numbers of MOSFETs being incorporated into the ECU, heightening the power density. The board sizes of ECUs never increase due to the cost implications, as it would call for retooling and prevent cross-utilization of the same electronics hardware across multiple car models. This fact is driving the industry to introduce smaller, more thermally efficient MOSFET packaging. Packages have changed from TO-220, to D2PAK, to DPAK, to the newer, more compact SO8FL options. But the smaller packages, and smaller semiconductor dies drive operating temperatures up - once again leading to reliability concerns

resurfacing, especially in the case of repetitive UIS (note that peak power in avalanche during an injection can be measured in kW).

Any question about the reliability of a car model can lead to dire consequences. It may result in expensive recalls being carried out and have huge impact on the manufacturer's branding. As a result, sourcing power components which have the high level specifications needed is vital.