Most modern power supplies are required to contain the harmonic content of the current they absorb from the line. Practically, regulations request the line current to be nearly sinusoidal and in phase with the line voltage. In this case, the Power Factor Correction (PFC) pre-regulator is typically inserted between the input bridge and the bulk capacitor. This intermediate stage is designed to output a constant dc voltage while drawing a sinusoidal current from the line. The step-up (or boost) configuration is generally adopted. This requires the output voltage to be higher than the maximum possible level of the line. For this reason the output regulation level is generally set to around 390 V in European or universal mains conditions.

Critical Conduction Mode (CRM) operation, also sometimes referred to as Boundary Conduction Mode (BCM), is the most popular solution for low power applications. This control method is characterized by a variable-frequency control scheme in which the inductor current first ramps to twice the desired line current, then ramps down to zero to eventually ramps positive again without dead-time (Figure 1). Implementing CRM requires circuitry to accurately detect the core reset of the inductor.

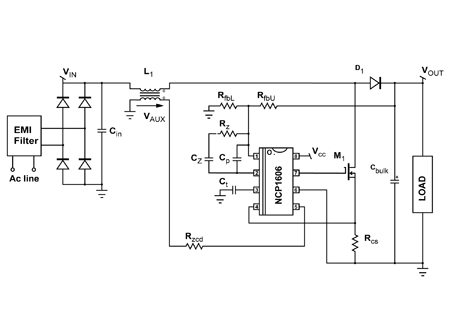

A popular technique for identifying the point at which complete demagnetization occurs is to monitor the inductor voltage to detect when the voltage drops to zero. However, monitoring the coil voltage directly is not an economical solution. Instead, a small winding called the "Zero-Current Detector" or ZCD winding is associated with the boost inductor to produce a scaled-down version of the inductor voltage that can be applied to the controller as shown in Figure 2. The ZCD winding is coupled so that it exhibits a negative voltage during the MOSFET conduction time (flyback configuration). This causes the ZCD voltage, VAUX, as shown in the waveform diagram of Figure 3 to vary according to:

, when the MOSFET is on

, when the MOSFET is on

, when the MOSFET is open

Where N is the turns ratio between the auxiliary and main windings

, when the MOSFET is open

Where N is the turns ratio between the auxiliary and main windings

The coil current reaches zero when VAUX begins to drop. Many CRM controllers compare VAUX to a ZCD reference close to 0V in order to detect this falling edge and thereby initiate the next turn-on signal for the output MOSFET at the correct time. A small amount of hysteresis is implemented for robust operation. In practice this creates an upper threshold, which is valid when VAUX rises, and a lower threshold effective when VAUX falls. For reasons such as the need to accommodate the multi-functionality of the ZCD pin of a PFC regulator such as the NCP1606, these thresholds are relatively high in most commercial parts available in the market. Practical thresholds are typically between 1 V and 2 V. As an example, the ZCD thresholds in the NCP1606 data sheet are specified as follows:

ZCD is a well established technique for implementing CRM control. However its accuracy can be compromised under high line conditions, when the AC supply voltage rises significantly above its nominal value. The corresponding increase in VIN results in a smaller value of VAUX during the demagnetization phase when the output MOSFET is turned off, since VAUX is proportional to the difference between the output and input voltages  at this time. This effect is illustrated in Figure 4, which also shows that the input voltage contains an AC component at the switching frequency. As a consequence of this, VAUX is not flat but exhibits a certain quantity of ripple. This is negligible at low line, but the reduction in VAUX amplitude seen at high line means these oscillations can take place at voltage levels that are in the range of the ZCD thresholds. This tends to degrade the accuracy of zero current detection.

at this time. This effect is illustrated in Figure 4, which also shows that the input voltage contains an AC component at the switching frequency. As a consequence of this, VAUX is not flat but exhibits a certain quantity of ripple. This is negligible at low line, but the reduction in VAUX amplitude seen at high line means these oscillations can take place at voltage levels that are in the range of the ZCD thresholds. This tends to degrade the accuracy of zero current detection.

Figure 4 portrays the VAUX voltage at high line, at the peak of the sinusoid where Vin is about 380V. The VAUX waveform shows the large ripple occurring during the demagnetization phase, which can cause the zero current comparator to trigger before the core is totally reset. This leads to instability of the line current, as shown in the red trace, as well as a degradation of power factor and, possibly, some audible noise. Figure 5 illustrates the effect of incorrect triggering of the zero current comparator. From time to time, the PFC stage starts a new cycle while the boost diode is still conducting, causing the circuit to operate in Continuous Conduction Mode (CCM).

This phenomenon can be reduced or suppressed by placing a resistor between VCC and the ZCD pin of the power-factor controller IC, as shown in Figure 6. By doing so, an offset is created on the ZCD pin.

In the application circuit shown, VCC is 15V and  . The addition of a

. The addition of a  resistor between VCC and the ZCD pin (pin 5), modifies the voltage applied to the ZCD pin.

The actual voltage that is applied to the ZCD pin during the demagnetization phase, representing the voltage across the ZCD winding, becomes:

resistor between VCC and the ZCD pin (pin 5), modifies the voltage applied to the ZCD pin.

The actual voltage that is applied to the ZCD pin during the demagnetization phase, representing the voltage across the ZCD winding, becomes:

Offsetting the voltage at the ZCD pin in this way has the same effect as comparing the VAUX voltage to ZCD thresholds that are reduced by 1.36V.

The new de facto ZCD thresholds are then:

Offsetting the voltage at the ZCD pin in this way has the same effect as comparing the VAUX voltage to ZCD thresholds that are reduced by 1.36V.

The new de facto ZCD thresholds are then:

High line voltages impair the accuracy of zero current detection, since unwanted CCM cycles can occur when the input voltage increases close to the output voltage. Noticeable effects are instability, degradation of power factor and possibly audible noise. Adding a resistor to offset the voltage presented at the ZCD pin of the power factor controller enhances the accuracy of zero current detection at high line, which can eliminate these issues. One further caveat to bear in mind is that the offset must stay below the minimum ZCD threshold of the power-factor controller IC, specified when the ZCD voltage is falling (VZCDL = 1.5V for the NCP1606). This is important to ensure that the offset ZCD threshold remains higher than 0V; otherwise the system may be unable to restart. For this reason, VCC variations should also be taken into account when determining the optimum value for the offset resistor. www.onsemi.com