Author:

Cliff Keys, Editor-in-Chief, Power Systems Design

Date

09/18/2010

I had the pleasure to meet with Marco Casale-Rossi, Product Marketing Manager, Galaxy Implementation Platform, Synopsys. Marco joined Synopsys in 2005, after 20 years at STMicroelectronics' Central R&D, where he participated in the development and deployment of one of the first "industrial" EDA solutions for ASIC implementation. Marco's most recent responsibility at ST was the management of the technology partnerships with EDA partners. Marco has contributed in building Synopsys' vision of the nanometer design and technology roadmap. Marco studied mathematics at the Università degli Studi di Milano, Italy, and computer science at the Politecnico di Milano, Italy.

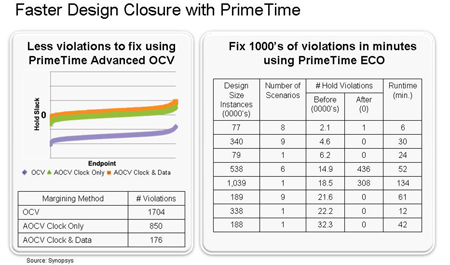

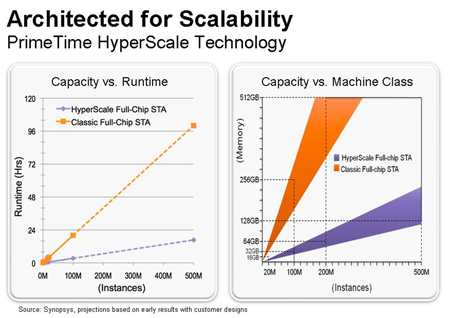

Synopsys unveiled new PrimeTime™ HyperScale technology that enables static timing analysis (STA) to scale beyond 500 million instances. PrimeTime HyperScale technology provides design engineers the insight required to solve many of the timing integration and closure problems they face with today's large system-on-chip (SoC) design flows while delivering a 5 to 10X boost in performance and capacity. PrimeTime HyperScale technology fits seamlessly with today's large SoC physical implementation flows where designs are implemented in blocks and then assembled at the chip-level for final timing closure and signoff. It improves the timing closure process by providing design engineers a better mechanism to look at block-level timing in the context of the full-chip timing earlier in the design process. By directly reusing block-level timing analysis and constraints, the HyperScale technology enables a 5 to10X boost in full-chip STA runtime and capacity without the accuracy limitations in current modeling techniques. Its auto generation capabilities provide design engineers with accurate and up-to-date timing contexts for the chip and block throughout the design process, leading to better decisions and enabling fewer iterations to reach timing closure.

The new PrimeTime HyperScale technology enhances the existing GalaxyTM Implementation Platform by providing more precise timing context to drive timing closure in IC Compiler. In addition, the HyperScale technology works with existing PrimeTime features like signal integrity (SI) analysis, advanced on-chip variation (AOCV) analysis, multi-scenario analysis and threaded multicore analysis, enabling design teams to further boost STA productivity and improve overall timing closure turn-around-time.

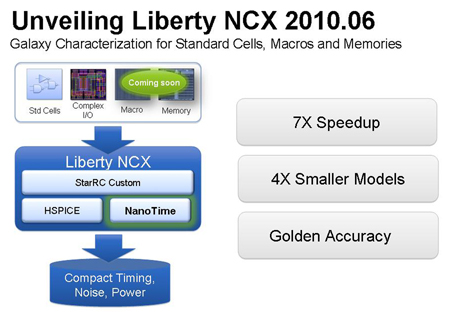

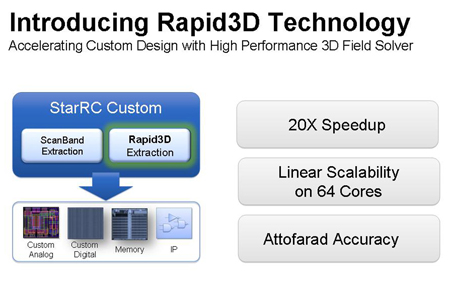

"As SoCs continue to increase exponentially in complexity, scalability of the design flow is a crucial factor in maintaining productivity," said Antun Domic, senior vice president and general manager, Synopsys Implementation Group. "By adding HyperScale technology, the 2010.06 release of PrimeTime includes a significant innovation to extend STA scalability for the next five to 10 years. This release represents an important milestone in delivering higher design team productivity both today and in the future." In related announcements today, Synopsys revealed two other productivity enhancements to its Galaxy Signoff product portfolio. New Rapid3D technology incorporated in Synopsys' StarRCTM Custom parasitic extraction solution provides up to a 20X extraction speedup for sub-45nm custom IC design and library characterisation. In addition, the latest release of LibertyTM NCX provides up to a 7X boost in characterisation speed while providing more efficient composite current source (CCS) models for IC Compiler physical implementation and PrimeTime timing analysis, enabling designers to quickly achieve timing closure and improve productivity.

The PrimeTime HyperScale technology is in limited customer availability and available to select customers in the PrimeTime SI 2010.06 release.

Comprehensive solution delivers golden accuracy and compact libraries Synopsys introduced its Galaxy Characterization Solution. The Galaxy Characterization Solution is a comprehensive suite of tools architected to generate compact, highly-accurate libraries for the design and implementation of complex system-on-chips (SoCs). Today's SoCs require libraries that contain hundreds of gigabytes of timing, power, noise and process variation data to ensure the chip meets all performance criteria. The Galaxy Characterization Solution is the only solution that can reduce the library size by an average of 4X and deliver precise timing, noise and power models for standard cells, macros and memories in the compact composite current source (CCS) library format.

The Galaxy Characterization Solution is based on Synopsys' golden-accuracy HSPICE® circuit simulation, technology-leading StarRC™ extraction, NanoTime transistor-level timing and Liberty™ NCX library modeling technologies. The compact CCS models generated by the solution feed seamlessly into the IC Compiler physical implementation and PrimeTime™ signoff tools, enabling designers to quickly achieve timing closure and improve productivity. As process geometries shrink to 28 nanometers (nm) and below and clock frequencies rise, it is essential to account for signal integrity (SI) and variation effects in the timing and noise model libraries to ensure proper silicon performance. As a result, library sizes can quickly explode from tens of gigabytes to hundreds of gigabytes. This poses a dilemma for the designer who needs accuracy but can't handle the enormity of the library or a potential increase in run time. To address this, Liberty NCX generates a compact CCS model that can reduce the library size by an average of 4X without impacting accuracy. In addition, Liberty NCX has been tuned for noise model generation, resulting in up to a 7X speedup. PrimeTime and IC Compiler readily process the compact CCS format, saving valuable run time, disk space and, ultimately, engineering costs. "Synopsys' unique combination of technology and innovative methodologies enables the Galaxy Characterization Solution to deliver a comprehensive characterisation capability that covers all aspects of designers' needs," said Dr. Antun Domic, senior vice president and general manager, Synopsys Implementation Group. "High-precision compact CCS models for power, timing and noise, combined with the seamless handoff to PrimeTime and IC Compiler allow designers to implement their SoC designs with a high degree of confidence." Today, the Galaxy Characterization Solution supports timing, power and noise models for standard cell libraries. Upcoming releases will provide timing and noise models for complex macros and embedded memories and will employ the NanoTime static timing engines to generate the results.

Rapid3D technology solves Sub-45nm extraction accuracy and runtime challengesfor custom IC design Synopsys, unveiled Rapid3D technology, a new 3D fast field solver engine fully integrated into Synopsys' StarRC™ Custom parasitic extraction solution. Building on the gold standard Raphael NXT engine, Rapid3D technology delivers attofarad accuracy and significant speedup by incorporating the latest advancements in 3D field solver algorithms. These algorithms take full advantage of modern multicore hardware to solve the accuracy and runtime challenges of sub-45nm extraction for custom IC design and IP characterisation.

Rapid3D technology is embedded as a standard feature in StarRC Custom, providing users proven reliability, leading parasitic modeling and standard interfaces to achieve silicon accuracy and improved productivity. On customer designs, the advanced Rapid3D algorithms have shown up to 20X runtime improvement in single processor core performance. In addition, Rapid3D technology has demonstrated near-linear multicore scalability, with up to an additional 54X boost in performance on 64 cores. The multicore technology takes advantage of optimised multi-threading to maximise throughput, even on memory-constrained compute resources. "Due to increasing parasitic effects at advanced process technologies, it is becoming harder to achieve accuracy and faster turnaround time for any leading-edge designs," said Eugene Chen, director of CAD engineering at Altera Corporation. "StarRC Custom with Rapid3D technology provides the speed and accuracy we need to help us achieve first-pass success and maintain a competitive advantage. In our evaluation, the Rapid3D technology delivered 13X faster runtime on a single CPU core." Synopsys developed the StarRC Custom Rapid3D technology to enable custom designers to not only achieve faster 3D extraction, but also empower them to accelerate overall design turnaround time through productivity links with Synopsys' technology-leading implementation, simulation and analysis solutions. These include integration with the Galaxy Custom Designer® solution for in-design 3D extraction, optimised links with the CustomSim™ simulator for high performance and high accuracy simulation of memory and SoC custom designs, and an interface with the NanoTime™ transistor-level timing analysis solution for signal integrity signoff of custom digital circuits. In addition, Rapid3D technology seamlessly connects with the new Liberty™ NCX solution (also announced today) to significantly speed up the development of more accurate, compact and performance-efficient libraries for Galaxy™ implementation and signoff tools, including the PrimeTime™ static timing analysis suite. "The introduction of StarRC Custom Rapid3D technology reinforces Synopsys' commitment to provide innovative technologies that deliver silicon accuracy as well as a significant reduction in design cycle time," said Bijan Kiani, vice president of product marketing at Synopsys. "The customer results we've seen to-date have been very encouraging, and we look forward to bringing this breakthrough technology to all StarRC Custom users."

StarRC Custom provides the foundation of Synopsys' extraction tool suite, which also includes StarRC and StarRC Ultra. StarRC Custom offers extraction for high-accuracy custom analog/mixed-signal (AMS) and digital designs. StarRC offers full-chip gate-level and transistor-level extraction, and StarRC Ultra supports advanced analysis capabilities. The tools incorporate technologies such as highly-scalable multicore processing, custom layout integration, hierarchical extraction, feature-scale chemical-mechanical polishing (CMP) effects modeling and variation-aware extraction to enable designers to achieve signoff accuracy while meeting their stringent tapeout schedules. www.synopsys.com